C7 @ 220uF is too small.

C7>= sqrt(2) * Cin * Rin / Rfb

>= 1.4 * 11 * 10k / 330 >= 471uF

That would improve low frequency distortion right? Distortion 8 as per Self.

Nicely done 5th,

I like the way you've mixed surface mount with TH but surface mounted the TH components - give me ideas. 🙂

I like the way you've mixed surface mount with TH but surface mounted the TH components - give me ideas. 🙂

A few optimisations of the schematic might help also:

1. R13 should be tied to GND not to -Vee

2. Put a capacitor at the base of Q3 tied to +Vcc to reduce the modulation of LTP current by VAS

3. In later schematics Self puts the capacitor C8 between C-E of Q7

EDIT: 4. I would lower the value of R22 also. This will increase transimpedance of the VAS.

Cheers,

Nesa

1. R13 should be tied to GND not to -Vee

2. Put a capacitor at the base of Q3 tied to +Vcc to reduce the modulation of LTP current by VAS

3. In later schematics Self puts the capacitor C8 between C-E of Q7

EDIT: 4. I would lower the value of R22 also. This will increase transimpedance of the VAS.

Cheers,

Nesa

Last edited:

This 3rd harmonic really looks suspicious in "favour" of C6.

If possible (still stable) i would take it out and see what happens to the 3rd harmonic plot.

Stable without performance the same.

Nicely done 5th,

I like the way you've mixed surface mount with TH but surface mounted the TH components - give me ideas. 🙂

Thanks 🙂

Hmm I thought that's what everyone would do >.< How else are you supposed to use some TH with surface mount otherwise 😀 Although I have drilled holes for the legs of the through holes to go through. They just solder on the top layer instead.

Chopping the legs off the through holes at just the right length and then holding them in place with tweezers isn't my idea of fun.

A few optimisations of the schematic might help also:

1. R13 should be tied to GND not to -Vee

As far as I know R13 is part of the two pole compensation circuit and should not be connected to ground. At least I've never seen it done that way.

2. Put a capacitor at the base of Q3 tied to +Vcc to reduce the modulation of LTP current by VAS

I could give that a go.

3. In later schematics Self puts the capacitor C8 between C-E of Q7

So it would seem.

EDIT: 4. I would lower the value of R22 also. This will increase transimpedance of the VAS.

That I've heard mentioned before about this amplifier.

I was thinking bigger SM pads and bend the leads to 90 degrees to sit on them.

How did you handle the electrolytic caps? Leave a space to reach in and solder?

How did you handle the electrolytic caps? Leave a space to reach in and solder?

I was thinking bigger SM pads and bend the leads to 90 degrees to sit on them.

How did you handle the electrolytic caps? Leave a space to reach in and solder?

Yeah they don't sit entirely flush with the board. It's the only drawback to this method.

Yeah they don't sit entirely flush with the board. It's the only drawback to this method.

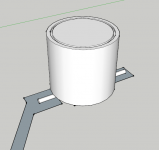

I'm thinking about something like this:

Bend the leads straight out on the caps and solder direct to a large pad on either side. A bit of fooling around making footprints for this but would beat the pudding out of drilling holes.

I'm thinking about something like this:

View attachment 155684

Bend the leads straight out on the caps and solder direct to a large pad on either side. A bit of fooling around making footprints for this but would beat the pudding out of drilling holes.

That's pretty much what a surface mount electrolytic looks like >.< Only everything is put together neatly, with a little square platic base that holds the thing upright and flat legs rather then round.

It's one area where surface mount falls behind through hole, their electrolytics, a lot of the time, take up a bigger footprint for an equally spec'd part.

Usually I try to use a surface mount part, but that can limit your selection quite severely, esp at farnell with electrolytics. I also swap to the odd through hole part if I need to take a trace to the bottom layer, or if I need to bridge over more then a couple of traces.

2. Put a capacitor at the base of Q3 tied to +Vcc to reduce the modulation of LTP current by VAS

Did not do anything.

EDIT: 4. I would lower the value of R22 also. This will increase transimpedance of the VAS.

Also didn't do anything.

What strikes me as odd is the third harmonic becoming more pronounced. If we look at the 8 v p-p plot vs the high output voltage one, you can see that all other harmonics actually go down with increasing drive level, second harmonic only rises by a little bit. (The fact the others go down is most likely due to the improved signal to noise ratio of a higher drive level though.)

The third harmonic becomes significantly more pronounced compared to the others and as a result stops following the distortion 'trend' IE distortion rising with increasing frequency beyond the compensation point. Whatever it is that's causing this third harmonic to appear is swamping whatever trend the amplifier is supposed to show. But this also shows that that same mechanic (amp trend) isn't degrading the performace even further, the 3rd is flatline from 20hz to 8khz.

Now this isn't degraded or changed in any way when the amplifier is forced to deliver current. It changes based entirely on what voltage is apparent on the output (or input or whatever). Coupling or crosstalk from one part to another, usually changes vs frequency. IE worse the higher you get, this isn't happening here though either.

This makes me think of the caps in the feedback network, or possibly the input caps. Although I can't imagine them being a problem, they're rated at 63V, but that's easy to test.

As I've said before the performance is, all things considered, still excellent. But what say any of you? What could be the cause of this? Could it be a measurement glitch?

I'm game for trying different components, just to make sure, in case something is dodgy.

Oh and Andrew I tried changing the large lytic in the feedback network, but that didn't alter anything.

As far as I know R13 is part of the two pole compensation circuit and should not be connected to ground. At least I've never seen it done that way.

You are right, I was watching IC datasheets lately and just re-accepted alternative way.

Did not do anything.

Also didn't do anything.

So, the main contributor of distortion is somewhere else.

I forgot to mention, but C9 seems to be a little high. Try values mentioned in Self's book. What are expected values of phase margin and unity loop gain?

Connect "lower" end of R13 to GND, not to -Ub...

Can anybody explain how this is supposed to lead to any advantage over the version shown (with the "lower" end connected to -Ub)?

And especially what this would change in repect to distortion?

I forgot to mention, but C9 seems to be a little high. Try values mentioned in Self's book. What are expected values of phase margin and unity loop gain?

With 150/330 pf we're at about 10 degrees by the time 100khz is reached. If that's what you were asking.

I'm not entirely sure how to simulate the unity loop gain. Are you asking for the open loop gain?

It is path from contamined -Ub bus (100Hz, half wave rectified signal..) to feedback path..Reference point for feedback is GND, not power bus.Can anybody explain how this is supposed to lead to any advantage over the version shown (with the "lower" end connected to -Ub)?

And especially what this would change in repect to distortion?

Performance can be like in attached graph, it is measured at very similar circuit, with TPC resistor conected to GND..

Attachments

Last edited:

It is path from contamined -Ub bus (100Hz, half wave rectified signal..) to feedback path..Reference point for feedback is GND, not power bus.

Performance can be like in attached graph, it is measured at very similar circuit, with TPC resistor conected to GND..

I'll try simulating that then perhaps give it a go. I am currently testing my TAS5630 build with the sample inductors from Ice components so watch this (class D forum) space.

The only thing I will say, is that the distortion performance measures pretty much the same (back to the slone amp now) with the amp driving no load or the 9.4 ohm test load.

Driving nothing there is very little on the power lines in the way of contaminants. At least hardly anything I can see, besides a very low level of ripple. Surely if stuff was being injected into the amp via the -ve rail, one would expect the distortion to get significantly worse once a load is connected? Because with a load connected I do see a lot more ripple and significant half sine wave pulses, but the distortion remains the same.

It can be one reason, not the only. You should go step by step to verify it. Second step can be to disconect overcurrent protection (disconect D2,D3). Can You post PCB picture ? Layout can be reason, too.

It can be one reason, not the only. You should go step by step to verify it. Second step can be to disconect overcurrent protection (disconect D2,D3). Can You post PCB picture ? Layout can be reason, too.

Aye I'll be posting the PCB in a bit, I've just got to edit it a little.

I removed the protection and it didn't change a thing, so at least it isn't that. I didn't think it was, but at least I can now be sure.

Okay here's the board layout. Green = copper top. The semi greyed out red is the copper bottom.

The black arrow points towards power ground.

The yellow arrow signal ground.

The blue arrow is the ground connection of the zobel. I didn't connect this anywhere as I wasn't sure where to connect it to.

Idea's I've had, of what to change are as follows.

Instead of having R1 where it is at point A, move it up to point B. The idea behind this to increase the distance of the power lines away from the input circuitry. The same would be done with C5, R5 and R6 ect. And I just noticed that I forgot to relabel Q3 and Q4 in the CCS, but no matter its obvious which they are.

Also I wasn't sure where to connect the protection circuitry to with regards to the output. At the moment the different parts of it connect in at C E and I. Should I reroute them to join at D and F?

Also G at the moment is the point where I take the NFB from. Now, providing it's in an adequate position, should I connect R10, R11 and C6 directly to this point. Or should I run the take off point back to point H and implement R10, R11 and C6 there instead?

Self makes mention of having a ground return mirroring the feedback path on the board, but instead run it on the copper bottom for example. He says that often you have the signal ground running down the middle of the board in this way. At one end you connect to the Star Point I would imagine. I am assuming this end to be near the input ground etc, IE the left hand side of the board with my layout. He then says the other end of it be used as the output ground ie the loudspeaker return path.

I can understand this, but he says that you should connect the loudspeaker return path directly to the Star point. So why say two things that are clearly different? Or am I missing the point?

You will want to open the schematic in a new window/tab to allow you to maximise it fully, otherwise it's a bit too small.

The black arrow points towards power ground.

The yellow arrow signal ground.

The blue arrow is the ground connection of the zobel. I didn't connect this anywhere as I wasn't sure where to connect it to.

Idea's I've had, of what to change are as follows.

Instead of having R1 where it is at point A, move it up to point B. The idea behind this to increase the distance of the power lines away from the input circuitry. The same would be done with C5, R5 and R6 ect. And I just noticed that I forgot to relabel Q3 and Q4 in the CCS, but no matter its obvious which they are.

Also I wasn't sure where to connect the protection circuitry to with regards to the output. At the moment the different parts of it connect in at C E and I. Should I reroute them to join at D and F?

Also G at the moment is the point where I take the NFB from. Now, providing it's in an adequate position, should I connect R10, R11 and C6 directly to this point. Or should I run the take off point back to point H and implement R10, R11 and C6 there instead?

Self makes mention of having a ground return mirroring the feedback path on the board, but instead run it on the copper bottom for example. He says that often you have the signal ground running down the middle of the board in this way. At one end you connect to the Star Point I would imagine. I am assuming this end to be near the input ground etc, IE the left hand side of the board with my layout. He then says the other end of it be used as the output ground ie the loudspeaker return path.

I can understand this, but he says that you should connect the loudspeaker return path directly to the Star point. So why say two things that are clearly different? Or am I missing the point?

You will want to open the schematic in a new window/tab to allow you to maximise it fully, otherwise it's a bit too small.

Attachments

Last edited:

- Status

- Not open for further replies.

- Home

- Amplifiers

- Solid State

- Slones 11.4 'Blameless'