No, the goal is to present a 1Meg resistive input to the probe -for low frequencies at least: at higher frequencies, the capacitance dominates-.

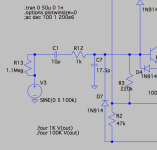

This is how to do it, but Ifind the VLF resistance disturbing low. The bootstrap might not work as intended in the sim. AFAIk, the physical circuit behaves as intended.

This is how to do it, but Ifind the VLF resistance disturbing low. The bootstrap might not work as intended in the sim. AFAIk, the physical circuit behaves as intended.