Well, I was working on this separately and this accelerated my work significantly, as I am playing with things at the moment. Further, above people have identified the place in CCES for setting the sample rate, along with in SigmaStudio. With my find on the memory settings in the files, and now having the video maker's files to load into CCES to see what they do, I am now closer to figuring out how to change this. The video maker assumes it is baked in, but how this works, often, is you have the crystal oscillator on the board, then you set the divisor in the firmware or software to then result in the appropriate sample rate. Now, there are ways where you can lock a board to a specific sample rate, such as doing a physical voltage divider to then do it, and that may be the case. If it is, then there has to be the inclusion of the asynchronous sample rate module.Sorry Google Translate.

I write in Russian - Пишу на русском.

В пакете представленном по ссылке на ГуглДиск есть утилита для записи готового проекта SigmaStudio (SS) в память DSP.

Вы невнимательно смотрели видео! Нужно четвертое видеоЭто не мои видео. Я не автор видео!

Я исследовал какой длины можно сделать FIR фильтр при текущих настройках на 96 kHz. Это 4000 тапов при 96 kHz. Больше получить нельзя!

Как переключить частоту на 48 kHz я не знаю!

Для чего на плате припаяна микросхема RAM на 8MB я не знаю. Подключить её я не смог.))

Расписываю тайминг ролика для записи проекта SigmaStudio (SS) в ROM DSP (как понимаю это память STM):

6:05 - перевод платы на управление из SS через USB-i переходник. Самый главный - это программа-прошивальщик CoreBoard Upgrade.exe

18:18 - начинается рассказ о том, что все настройки только в RAM и пропадут при выключении питания.

18:50 - нужно экспортировать свой проект из SS.

19:12 - экспорт проекта (Export System Files) из SS в нужный для прошивальщика CoreBoard Upgrade.exe

19:22 - экспортируемые файлы SS записываем в папку прошивальщика \Sigma_Files\

Существующие в папке файлы нужно удалить, чтобы папка была чистой перед записью вашего проекта!!!

20:13 - после экспорта файлов, подключаем плату процессора напрямую к USB!

USBi отключаем!!!

20:39 - запускаем CoreBoard Upgrade.exe и нажимаем на кнопку Sigma_Files

21:38 - запись пошла.

21:54 - всё, запись прошла успешно в ROM DSP и теперь выключение питания ничего не сбросит.

Если вам не нужны FIR фильтры, то лучше использовать китайскую оболочку, которая идёт с платой.

В SS ещё нужно разобраться в нумерацией выходов ADC, а она случайная.))

Потом, если нет программы SS записанной в ROM, то возможны неожиданные щелчки на полную громкость - это пугает.

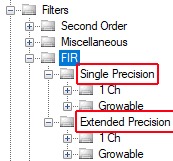

Further, are you using enhanced FIR or simple? I tried the higher precision FIR filtering in a prior schematic and could barely get the same as you. But by using single precision FIR filtering, I got to a larger number. Have you tried using single precision on the FIR filters?

And I have capacitor filters on my tweeters. So less scary than most, but FIR filtering live is why I bought these.

So, this is the google translate from the text documents in the folder from the video:

Module board DSP interface definition description

Module

FS(96KHz) A11

CLK(6.144MHz) A8

Master CLK(24.576MHz) A14

IN A/B A9

IN C/D A5

OUT1/2 A6

OUT3/4 A10

OUT5/6 A20

OUT7/8 A15

IN E/F A16

IN G/H A18

IN I/J(S/PDIF) A17(S/PDIF)

OUT9/10(S/PDIF) A12

A: The factory default is a complete audio processor program with 4 inputs and 8 outputs. It can be controlled by connecting the USB port of the computer and the MICRO USB interface of the core board using the Yinjili DSP control software, which is suitable for final products or general DIYers. The USBI interface is disabled in this mode, so this module cannot modify the program or add other algorithms through SIGMASTUDIO by itself.

B: If you need to redesign or add new algorithm modules by yourself, please follow the steps below:

1. Open the Yinjili DSP upgrade tool, click the "Upgrade MCU" button, and upgrade the "custom algorithm.hex" in the Mcu_Files folder;

2. Open adsp21489_10in_10out.dspproj under the Sigma_Files folder, make modifications on this basis, connect the USBI, press F7, listen or test, and confirm that the project is OK;

3. Press Shift+Alt+A and select Export System Files to export the file;

4. Click Yinjili DSP upgrade tool.exe, select the upgrade project, and run it independently after the progress bar is finished.

Note: After customizing the algorithm, the PC control software will not be able to control the core board.

Of course, we can continuously switch between factory presets and custom algorithms. If you need to switch back to the factory program, please pay attention to the WeChat public account: Yinjili Technology Reply: You can get the factory program after leaving the factory.

Factory reset:

1. Download the two folders (Mcu_Files and Sigma_Files), and replace the folder with the same name under the original DSP Module Data of Yinjili Technology (please delete the original Mcu_Files and Sigma_Files folders first)

2. Open the Yinjili DSP upgrade tool, click the "Upgrade MCU" button, and upgrade the "factory program.hex" in the Mcu_Files folder;

3. Select the upgrade project again. After the progress bar is finished, you can use the PC control.

Document 2

Upgrade Instructions

It should be noted that the MCU of this board does not open the interface to the outside world, do not try to modify/read or reprogram it. How to use the core board custom mode:

A: The factory default is a complete audio processor program with 4 inputs and 8 outputs. It can be controlled by connecting the USB port of the computer and the MICRO USB interface of the core board using the Yinjili DSP control software, which is suitable for final products or general DIYers. The USBI interface is disabled in this mode, so this module cannot modify the program or add other algorithms through SIGMASTUDIO by itself.

B: If you need to redesign or add new algorithm modules by yourself, please follow the steps below:

1. Open CoreBoard_Upgrade.exe, click the "Mcu_Files" button, and upgrade "Custom mode_For usbi.hex" in the Mcu_Files folder;

2. Open adsp21489_10in_10out.dspproj under the Sigma_Files folder, make modifications on this basis, connect the USBI, press F7, listen or test, and confirm that the project is OK;

3. Press Shift+Alt+A and select Export System Files to export the file;

4. Open CoreBoard_Upgrade.exe, click Sigma_Files, and run it independently after the progress bar is finished.

Note: After customizing the algorithm, the PC control software will not be able to control the core board. If external control is required, please connect USBI (SPI interface) to control the dsp.

Factory reset of the core board (normal mode):

1. Unzip the Sigma_Files.rar (factory project file) in the Sigma_Files folder, and replace the project file generated after the custom mode.

2. Open CoreBoard_Upgrade.exe, click Sigma_Files/ in turn, first upgrade the factory project files, then click the "Mcu_Files" button, and select Normal mode For PC.hex

3. After the progress bar is finished, you can use the PC control.

Document 3

Instructions on power supply for the test backplane

In order to test DSP and ADDA, you can buy our power supply board and test backplane. The power supply interface of the test backplane has a total of 7P, labelled CN8, and the voltage of each PIN is marked on the silk screen, but the voltage does not represent the actual input value, and the correction is as follows: The input voltage of -12V terminal needs to be greater than -15V, because it has undergone a first-level voltage regulation later, and it is regulated to -12V by JRC7912; The input voltage of +12V terminal needs to be greater than +15V, because it is regulated by a first-level voltage regulator later, and it is regulated to -12V by JRC7812; The input voltage of the A+5V/D+5V terminal needs to be greater than +6.5V, because it has undergone a first-level voltage regulation later, and the AMS1086-5.0 is used to regulate it to +5V; 3V0 terminal is not used.

If there is no suitable voltage input, the machine will be damaged or the indicators will be deteriorated. It is recommended to buy an additional power supply board with our matching unit price of 28 yuan. If you only have a 12V/+5V regulated module power supply, you can try to short-circuit the 3-terminal regulated module, or you can use it.

Module board DSP interface definition description

Module

FS(96KHz) A11

CLK(6.144MHz) A8

Master CLK(24.576MHz) A14

IN A/B A9

IN C/D A5

OUT1/2 A6

OUT3/4 A10

OUT5/6 A20

OUT7/8 A15

IN E/F A16

IN G/H A18

IN I/J(S/PDIF) A17(S/PDIF)

OUT9/10(S/PDIF) A12

A: The factory default is a complete audio processor program with 4 inputs and 8 outputs. It can be controlled by connecting the USB port of the computer and the MICRO USB interface of the core board using the Yinjili DSP control software, which is suitable for final products or general DIYers. The USBI interface is disabled in this mode, so this module cannot modify the program or add other algorithms through SIGMASTUDIO by itself.

B: If you need to redesign or add new algorithm modules by yourself, please follow the steps below:

1. Open the Yinjili DSP upgrade tool, click the "Upgrade MCU" button, and upgrade the "custom algorithm.hex" in the Mcu_Files folder;

2. Open adsp21489_10in_10out.dspproj under the Sigma_Files folder, make modifications on this basis, connect the USBI, press F7, listen or test, and confirm that the project is OK;

3. Press Shift+Alt+A and select Export System Files to export the file;

4. Click Yinjili DSP upgrade tool.exe, select the upgrade project, and run it independently after the progress bar is finished.

Note: After customizing the algorithm, the PC control software will not be able to control the core board.

Of course, we can continuously switch between factory presets and custom algorithms. If you need to switch back to the factory program, please pay attention to the WeChat public account: Yinjili Technology Reply: You can get the factory program after leaving the factory.

Factory reset:

1. Download the two folders (Mcu_Files and Sigma_Files), and replace the folder with the same name under the original DSP Module Data of Yinjili Technology (please delete the original Mcu_Files and Sigma_Files folders first)

2. Open the Yinjili DSP upgrade tool, click the "Upgrade MCU" button, and upgrade the "factory program.hex" in the Mcu_Files folder;

3. Select the upgrade project again. After the progress bar is finished, you can use the PC control.

Document 2

Upgrade Instructions

It should be noted that the MCU of this board does not open the interface to the outside world, do not try to modify/read or reprogram it. How to use the core board custom mode:

A: The factory default is a complete audio processor program with 4 inputs and 8 outputs. It can be controlled by connecting the USB port of the computer and the MICRO USB interface of the core board using the Yinjili DSP control software, which is suitable for final products or general DIYers. The USBI interface is disabled in this mode, so this module cannot modify the program or add other algorithms through SIGMASTUDIO by itself.

B: If you need to redesign or add new algorithm modules by yourself, please follow the steps below:

1. Open CoreBoard_Upgrade.exe, click the "Mcu_Files" button, and upgrade "Custom mode_For usbi.hex" in the Mcu_Files folder;

2. Open adsp21489_10in_10out.dspproj under the Sigma_Files folder, make modifications on this basis, connect the USBI, press F7, listen or test, and confirm that the project is OK;

3. Press Shift+Alt+A and select Export System Files to export the file;

4. Open CoreBoard_Upgrade.exe, click Sigma_Files, and run it independently after the progress bar is finished.

Note: After customizing the algorithm, the PC control software will not be able to control the core board. If external control is required, please connect USBI (SPI interface) to control the dsp.

Factory reset of the core board (normal mode):

1. Unzip the Sigma_Files.rar (factory project file) in the Sigma_Files folder, and replace the project file generated after the custom mode.

2. Open CoreBoard_Upgrade.exe, click Sigma_Files/ in turn, first upgrade the factory project files, then click the "Mcu_Files" button, and select Normal mode For PC.hex

3. After the progress bar is finished, you can use the PC control.

Document 3

Instructions on power supply for the test backplane

In order to test DSP and ADDA, you can buy our power supply board and test backplane. The power supply interface of the test backplane has a total of 7P, labelled CN8, and the voltage of each PIN is marked on the silk screen, but the voltage does not represent the actual input value, and the correction is as follows: The input voltage of -12V terminal needs to be greater than -15V, because it has undergone a first-level voltage regulation later, and it is regulated to -12V by JRC7912; The input voltage of +12V terminal needs to be greater than +15V, because it is regulated by a first-level voltage regulator later, and it is regulated to -12V by JRC7812; The input voltage of the A+5V/D+5V terminal needs to be greater than +6.5V, because it has undergone a first-level voltage regulation later, and the AMS1086-5.0 is used to regulate it to +5V; 3V0 terminal is not used.

If there is no suitable voltage input, the machine will be damaged or the indicators will be deteriorated. It is recommended to buy an additional power supply board with our matching unit price of 28 yuan. If you only have a 12V/+5V regulated module power supply, you can try to short-circuit the 3-terminal regulated module, or you can use it.

BTW, is anyone a native Chinese speaker or a user of wechat? The company's name is 音极丽科技 (Yinjili Technology). The document 1 said they have a public wechat account. This may be the best place to receive answers on software, on changing sample rates, etc. So, the next step is to contact the company, but I do not have a wechat account, don't want to put the app on my phone, and the app for desktop has QR code to log you in from your phone, which I refuse to use QR codes on principle! As such, I'm reaching out to see if anyone else wants to do so. I will if no one else steps up. We should also make a list of questions to be asked.

1) updated firmware for the device

2) Does the redesigned backbone board effect the mainboard regarding software?

3) for SPDIF on the new board, is it in or out, does it require the bias voltage on the same header, etc?

4) what settings need set in Sigmastudio to have analog in and digital SPDIF in at the same time?

5) can we get a standard image of the sigmastudio hardware control panel to have as a permanent image from the company for the settings on that screen (talking with the input channels, the input-output mode and allowable settings, the hex addresses, the memory size settings, etc.)? Also to let us know which settings can be changed in that menu.

6) Is there a way to change the sample rate from 96kHz to 48kHz?

7) Do they have a "custom board support file" for use with CCES to develop custom applications?

If anyone can think of anything else that needs asked directly from the manufacturer, speak up. I don't know if I will reach out tonight, but probably will soon-ish. Still have to finish tracking down the company on wechat to ask. But with a company name and a pointer to where to contact them, I've contacted foreign companies with less.

1) updated firmware for the device

2) Does the redesigned backbone board effect the mainboard regarding software?

3) for SPDIF on the new board, is it in or out, does it require the bias voltage on the same header, etc?

4) what settings need set in Sigmastudio to have analog in and digital SPDIF in at the same time?

5) can we get a standard image of the sigmastudio hardware control panel to have as a permanent image from the company for the settings on that screen (talking with the input channels, the input-output mode and allowable settings, the hex addresses, the memory size settings, etc.)? Also to let us know which settings can be changed in that menu.

6) Is there a way to change the sample rate from 96kHz to 48kHz?

7) Do they have a "custom board support file" for use with CCES to develop custom applications?

If anyone can think of anything else that needs asked directly from the manufacturer, speak up. I don't know if I will reach out tonight, but probably will soon-ish. Still have to finish tracking down the company on wechat to ask. But with a company name and a pointer to where to contact them, I've contacted foreign companies with less.

So, the ICE-1000, which is basically the ICE-100b, is the 5MHz variant and you can buy those for around $200 on mouser/digi/etc. The 40MHz version is ICE-2000, is over $1000, and is a different beast. The cheap ones I saw on ebay are of the ICE-1000 type. So it depends. Now, this JTAG ICE (in-circuit emulator is what ICE stands for) would also be usable if you wanted to, in the future, buy the eval boards directly from ADI or on the other parts websites, with it being about $450 (when you can find them in stock) for the new ADSP-21593, which has the power of 4 x ADSP-21489. And the carrying board is able to work with other main boards, so swapping in the future drops down to $100-200 instead of replacing everything (if wanting to do upgrade-able down the line).

FIrst welcome ajc9988 and glad to have you here

I also found the same ICE-1000 on ebay, waiting for funds to get one

Well my question was are we able to do the same - does ICE-1000 have same functionality as ICE-2000 just slower? Seems so but not 100% sure

BTW, is anyone a native Chinese speaker or a user of wechat? The company's name is 音极丽科技 (Yinjili Technology). The document 1 said they have a public wechat account. This may be the best place to receive answers on software, on changing sample rates, etc. So, the next step is to contact the company, but I do not have a wechat account, don't want to put the app on my phone, and the app for desktop has QR code to log you in from your phone, which I refuse to use QR codes on principle! As such, I'm reaching out to see if anyone else wants to do so. I will if no one else steps up. We should also make a list of questions to be asked.

1) updated firmware for the device

2) Does the redesigned backbone board effect the mainboard regarding software?

3) for SPDIF on the new board, is it in or out, does it require the bias voltage on the same header, etc?

4) what settings need set in Sigmastudio to have analog in and digital SPDIF in at the same time?

5) can we get a standard image of the sigmastudio hardware control panel to have as a permanent image from the company for the settings on that screen (talking with the input channels, the input-output mode and allowable settings, the hex addresses, the memory size settings, etc.)? Also to let us know which settings can be changed in that menu.

6) Is there a way to change the sample rate from 96kHz to 48kHz?

7) Do they have a "custom board support file" for use with CCES to develop custom applications?

If anyone can think of anything else that needs asked directly from the manufacturer, speak up. I don't know if I will reach out tonight, but probably will soon-ish. Still have to finish tracking down the company on wechat to ask. But with a company name and a pointer to where to contact them, I've contacted foreign companies with less.

I was thinking about same also, but I think instead of asking batch of specific questions for his old project (2018), maybe it would be possible to get Their CCES/VDSP source codes(Yes, Im sure they have custom ones). That should sort out most if not all problems, and speed up everything. Whatever info we would need we could read it from source.. and change what we want instead of building, configuring ourselves.

I found shop address also in schematics:

https://shop67146674.taobao.com/

About SPDIF

What I found in one of text files:

IN I/J(S/PDIF) A17(S/PDIF)

OUT9/10(S/PDIF) A12

So it seems both in and out are working out of the box when it comes to firmware

Changing the sample rate from 96kHz to 48kHz?

Yes Im pretty sure its as you pointed out crystal value and divisor in some CCES file + settings in CCES and SigmaStudio.

I am using just DSP board without their Motherboard or DAC/ADC, I use my own inputs and outputs via I2S

I have it connected with CM6632A XMOS (In slave mode) and https://www.diyinhk.com/shop/audio-...84khz-32bit-es9016-pcm-dxd-dsd-audio-dac.html

For more flexibility and comfort I want to add bluetooth input, rotary encoder (input select and volume control of dac via i2c registers - more like mute function acutally, oled or lcd screen) So experience is as it is finished product

Was really easy to set up, had most of functionality.. except one - resampling of bluetooth and it seems impossible to be done on ALSA so also on most popular audio streaming distros - cannot feed SHARC DSP board with 44.1k, need to be 96k (on vendor firmware)

So I ordered ESP32 will play with it.. other option for me is Qualcomm bluetooth CSRA6620(or similar) + programmer (this one have resampling done in hardware)

and think best option - Enable ASRC on DSP board

SHARC also have FIR accelerator.. not sure its enabled by default, think it needs special version of algo in SigmaStudio

1) as to the difference in ICE-1000 and ICE-2000, the speed is the main thing I've seen listed as being different. I'm sure there are other differences, but that is a big one on specs. But, both are listed as working on all projects up to the current SC594 and ADSP-21593 chips. So if you plan to buy more or continue working with analog devices products, an ICE-1000 is a good addition. Which the ADSP-SC594 is their new arm+sharc core and the 21593 is their new sharc+ core. Both have about 4x the processing of the 21489. That is what is coming down the track. (I've spent too much time on analog devices website looking up specs, etc.).FIrst welcome ajc9988 and glad to have you here

I also found the same ICE-1000 on ebay, waiting for funds to get oneThere was also what I understand a clone of ICE-2000 for $350 .. now website seems down.. maybe its temporary, was working just like 2 weeks ago - http://opendsp.cn/

Well my question was are we able to do the same - does ICE-1000 have same functionality as ICE-2000 just slower? Seems so but not 100% sure

I was thinking about same also, but I think instead of asking batch of specific questions for his old project (2018), maybe it would be possible to get Their CCES/VDSP source codes(Yes, Im sure they have custom ones). That should sort out most if not all problems, and speed up everything. Whatever info we would need we could read it from source.. and change what we want instead of building, configuring ourselves.

I found shop address also in schematics:

https://shop67146674.taobao.com/

View attachment 1067069

About SPDIF

What I found in one of text files:

IN I/J(S/PDIF) A17(S/PDIF)

OUT9/10(S/PDIF) A12

So it seems both in and out are working out of the box when it comes to firmware

View attachment 1067073

Changing the sample rate from 96kHz to 48kHz?

Yes Im pretty sure its as you pointed out crystal value and divisor in some CCES file + settings in CCES and SigmaStudio.

I am using just DSP board without their Motherboard or DAC/ADC, I use my own inputs and outputs via I2S

I have it connected with CM6632A XMOS (In slave mode) and https://www.diyinhk.com/shop/audio-...84khz-32bit-es9016-pcm-dxd-dsd-audio-dac.html

View attachment 1067084

For more flexibility and comfort I want to add bluetooth input, rotary encoder (input select and volume control of dac via i2c registers - more like mute function acutally, oled or lcd screen) So experience is as it is finished productI had raspberryPi hooked up as input with various distros like volumio, moode audio etc.

Was really easy to set up, had most of functionality.. except one - resampling of bluetooth and it seems impossible to be done on ALSA so also on most popular audio streaming distros - cannot feed SHARC DSP board with 44.1k, need to be 96k (on vendor firmware)

So I ordered ESP32 will play with it.. other option for me is Qualcomm bluetooth CSRA6620(or similar) + programmer (this one have resampling done in hardware)

and think best option - Enable ASRC on DSP board

SHARC also have FIR accelerator.. not sure its enabled by default, think it needs special version of algo in SigmaStudio

2) Obviously if they are willing to give us the source code and CCES/VDSP+ files to modify and build off of their work, that would be optimal. We shall see when we contact them what they can give.

3) I was pretty sure the SPDIF was working. What I noticed is the number of inputs is 10. What that means is the SPDIF input supports 6 channels of audio. So it isn't just wired up, if you are looking at 5.1 signal from spdif, this can handle it. It also means we need to ask to be sure, but most likely we can set the project to analog/digital coexistence in SigmaStudio. In another help thread on Analog's website, they mentioned their scheme for listing inputs is analog inputs first, digital inputs after that. So the first four inputs should all be the analog inputs. Don't know if that was made clear since someone mentioned the assignment is random (everything in electronics is planned, not random). But thank you for digging through the schematics. It's more evidence to bolster my assumptions.

4) I agree that ASRC on the DSP board would be best. But if it hasn't been implemented, and until we implement it, matching sample rates can be a pain. But that is GiAntz big driving force and is a concern of mine (and all of ours, it seems).

5) I like your setup. Quite nice. I have more to do as mine is getting strapped to an L bracket strapped to a self-made plate amp. I'll have 3 power supplies (already checked the power supply for this board and the Arylic Up2Stream Pro v3 can take the inrush of current by the power supply for the amplifier units. The power supply for the amplifier units is a 48V DC, 800W continuous, which the drivers added together doubling their RMS is within the continuous rating of the power supply. But that takes up that, then the shelf of power supplies and the Arylic. Then the DSP on the shelf. Then the amplifier units with a large heatsink on the other side of the plate for those (TPA3255 amplifiers for now). The Arylic allows for connecting by bluetooth, but streams the stuff from the internet, so less delay issues from bluetooth. But since the Arylic acts as the preamp for the system (including use of a remote for volume control), that solves a fair amount of my issues. But, the problem of Arylic is the sample rate. So it should pass through the analog signal, but the digital signal will go over SPDIF.

I considered doing the RPI4, but then changed directions. Instead the RPI4 I bought will now be used as a signal generator for display calibration (I have the i1pro2 and i1Display Pro).

6) SHARC does have FIR accelerators. So that isn't as much of an issue. I do have all SigmaStudio for SHARC addins and plugins installed. Also, using CCES 2.11 has a newer compiler engine in it that allows for extra taps. So upgrading that is worthwhile.

https://www.arylic.com/products/up2stream-pro-receiver-board

Yes, convoluted whether it is you or us doing the google translate. But I do appreciate your contributions on the topic.Good. But everything will be through Google Translate.

1. Yes I plan to buy ICE-1000. Honestly I didnt know its such big difference in performance in their DSP.. I couldnt find any benchmarks.. so I just thought they are similar - 2 cores 300Mhz - 450Mhz is most of them.. 4 times is a lot, nice finding.1) as to the difference in ICE-1000 and ICE-2000, the speed is the main thing I've seen listed as being different. I'm sure there are other differences, but that is a big one on specs. But, both are listed as working on all projects up to the current SC594 and ADSP-21593 chips. So if you plan to buy more or continue working with analog devices products, an ICE-1000 is a good addition. Which the ADSP-SC594 is their new arm+sharc core and the 21593 is their new sharc+ core. Both have about 4x the processing of the 21489. That is what is coming down the track. (I've spent too much time on analog devices website looking up specs, etc.).

2) Obviously if they are willing to give us the source code and CCES/VDSP+ files to modify and build off of their work, that would be optimal. We shall see when we contact them what they can give.

3) I was pretty sure the SPDIF was working. What I noticed is the number of inputs is 10. What that means is the SPDIF input supports 6 channels of audio. So it isn't just wired up, if you are looking at 5.1 signal from spdif, this can handle it. It also means we need to ask to be sure, but most likely we can set the project to analog/digital coexistence in SigmaStudio. In another help thread on Analog's website, they mentioned their scheme for listing inputs is analog inputs first, digital inputs after that. So the first four inputs should all be the analog inputs. Don't know if that was made clear since someone mentioned the assignment is random (everything in electronics is planned, not random). But thank you for digging through the schematics. It's more evidence to bolster my assumptions.

4) I agree that ASRC on the DSP board would be best. But if it hasn't been implemented, and until we implement it, matching sample rates can be a pain. But that is GiAntz big driving force and is a concern of mine (and all of ours, it seems).

5) I like your setup. Quite nice. I have more to do as mine is getting strapped to an L bracket strapped to a self-made plate amp. I'll have 3 power supplies (already checked the power supply for this board and the Arylic Up2Stream Pro v3 can take the inrush of current by the power supply for the amplifier units. The power supply for the amplifier units is a 48V DC, 800W continuous, which the drivers added together doubling their RMS is within the continuous rating of the power supply. But that takes up that, then the shelf of power supplies and the Arylic. Then the DSP on the shelf. Then the amplifier units with a large heatsink on the other side of the plate for those (TPA3255 amplifiers for now). The Arylic allows for connecting by bluetooth, but streams the stuff from the internet, so less delay issues from bluetooth. But since the Arylic acts as the preamp for the system (including use of a remote for volume control), that solves a fair amount of my issues. But, the problem of Arylic is the sample rate. So it should pass through the analog signal, but the digital signal will go over SPDIF.

I considered doing the RPI4, but then changed directions. Instead the RPI4 I bought will now be used as a signal generator for display calibration (I have the i1pro2 and i1Display Pro).

6) SHARC does have FIR accelerators. So that isn't as much of an issue. I do have all SigmaStudio for SHARC addins and plugins installed. Also, using CCES 2.11 has a newer compiler engine in it that allows for extra taps. So upgrading that is worthwhile.

https://www.arylic.com/products/up2stream-pro-receiver-board

2. Yes would be optimal, for GiAnt1961 would be just changing couple values to sort out his problems. For us getting ASRC working also shouldnt take long.

If we dont get source code.. I think its still doable in reasonable time.. board itself is simple/basic - RAM, SPI FLASH, thats about it. How hard it can be?

Only mystery for me is STM32 chip, at first I thought its only for programming SPI FLASH/EEPROM but from schematics it seems USBi dongle is connected to this chip. Also I checked miniSHARC board - no stm32 there. Will custom code in STM32 will be problem? No idea.. we will see

By the way I seen variant of this board with EEPROM not SPI Flash, so there should be other version of firmware somewhere.

3. Maybe its possible to do 5.1 audio, but you would need dolby decoder in firmware (license needed?), and decoding also takes compute power and its not lossless.. anyway active crossover + 5.1 audio is more trouble than I want now

5. Thanks

*For me PC->XMOS will be 'high quality' connection - thats music source.

*Bluetooth, to connect TV so watch some netflix or hbo, or connect phone if I want to play 'quick' -- So I dont care that much about quality or delay here, as long its not terrible. Its an extra input for me.

6. Good to know, think I have older version, will need to upgrade

1) https://www.analog.com/en/parametricsearch/11131#/sort=71,desc1. Yes I plan to buy ICE-1000. Honestly I didnt know its such big difference in performance in their DSP.. I couldnt find any benchmarks.. so I just thought they are similar - 2 cores 300Mhz - 450Mhz is most of them.. 4 times is a lot, nice finding.

2. Yes would be optimal, for GiAnt1961 would be just changing couple values to sort out his problems. For us getting ASRC working also shouldnt take long.

If we dont get source code.. I think its still doable in reasonable time.. board itself is simple/basic - RAM, SPI FLASH, thats about it. How hard it can be?

Only mystery for me is STM32 chip, at first I thought its only for programming SPI FLASH/EEPROM but from schematics it seems USBi dongle is connected to this chip. Also I checked miniSHARC board - no stm32 there. Will custom code in STM32 will be problem? No idea.. we will see

By the way I seen variant of this board with EEPROM not SPI Flash, so there should be other version of firmware somewhere.

3. Maybe its possible to do 5.1 audio, but you would need dolby decoder in firmware (license needed?), and decoding also takes compute power and its not lossless.. anyway active crossover + 5.1 audio is more trouble than I want nowThink on board we have all Inputs/outputs are digital - I2s/spdif (Or I dont understand something

) and SHARC have 20 fully programmable pins for our inputs and outputs. They are arranged in groups called SPORTs and If I got it right then maybe its possible to make 1 Input ASRC, other 1:1 .. that would be great

(maybe, that would have to be checked) ASRC solve some problems and make connecting easy as LEGO but produce new 'problems' like bit perfect is gone, compute power needed for resampling? a lot of power if you want good resampling?

5. ThanksWould like to see what you got there also

I was thinking about TPA3255 also or the ICEpower

*For me PC->XMOS will be 'high quality' connection - thats music source.

*Bluetooth, to connect TV so watch some netflix or hbo, or connect phone if I want to play 'quick' -- So I dont care that much about quality or delay here, as long its not terrible. Its an extra input for me.

6. Good to know, think I have older version, will need to upgrade

Look on that chart at the MMACS (millions of multiply accumulate calculations per second) rating. You will find the fastest version of the 21489 does 900 MMACS. Meanwhile, the new SC594 and 21593 do 4000 MMACS. Because of Intel being the speed demon for decades, people focus on frequency, which the 21489 is rated around 450MHz and the two new ones are 1GHz (they have 800Mhz variants) and dual core. Either way, you look to instructions per second (like MMACS) to figure out the actual compute power. With nearly double the frequency, along with double the cores, it is easy to tell how they arrived at over 4x the calculation power versus the older 21489. As such, they are potent, and I cannot wait for them to become mainstream.

2) I really want the ASRC, as having that on the fly is the most user friendly way to implement it.

And that is good to know on the variant. I haven't dove into the schematics as much yet (playing catch up now that I have this information at hand.

3) Yes, I personally do not want 5.1 through SPDIF, but I did like that this is an option (even if I don't want it). As to you doing the mainboard with the processor, you are right. All are digital at that point. But, I was meaning the backplane and DAC/ADCs that you can buy with their product, which has 4 analog input on it. The way those are supposed to be wired to the processor is to have the analog first in the list of inputs, then the digital inputs. But, that is still dependent on the manufacturer implementing the tracings in that way. And I have not compared the schematics to the ADSP-21489 data sheet yet.

As to the SPORTs, I saw at least one mention using those to create external controls connected to potentiometers. Something to keep in mind.

Regarding ASRC on one and not the other input, it most likely would be applied to all signals with passthrough if the rates match that of the device. But it should be lego like, which is how they have made sigmastudio for batches of code. You could optimize coding if doing from scratch instead of code batches that get plugged in, but that is a different conversation.

5. as to that, once I get it done, pictures will be shared! As to icepower, ONLY buy their new 300A2 or 400A2. Both have good properties on low distortion. The rest are not that great. I got the 3EAudio https://www.3e-audio.com/amplifier-kits/tpa3255-2ch-260w/

I cannot find the original design now, but those are $165 each. But there are numerous designs that are noteworthy with the TPA3255.

6. Yep, why I mentioned it. When I tested how many taps it allows with 2.10 and 2.11, and then double checked the engine of the compiler being updated, it has to be more efficient compiling that allows for more instructions.

So, after I changed the sigmastudio values to match those in the video, then it reduces it to only 4,000 taps for FIR filtering. So either that much memory is taken by other things, or they really went with a much smaller memory size drastically reducing the amount of correction available. I recommend using the DIRAC method anyways, of first correcting the signal with IIR filters, which are cheap computationally, then using FIR only to correct the linear phase and some minor frequency correction. That will make it more effective overall.Good. But everything will be through Google Translate.

I really need to contact the company though for more.

1. Okay, didnt see this chart, I only found that 'The ADSP-21489 offers the highest performance – 450 MHz / 2700 MFLOPs'1) https://www.analog.com/en/parametricsearch/11131#/sort=71,desc

Look on that chart at the MMACS (millions of multiply accumulate calculations per second) rating. You will find the fastest version of the 21489 does 900 MMACS. Meanwhile, the new SC594 and 21593 do 4000 MMACS. Because of Intel being the speed demon for decades, people focus on frequency, which the 21489 is rated around 450MHz and the two new ones are 1GHz (they have 800Mhz variants) and dual core. Either way, you look to instructions per second (like MMACS) to figure out the actual compute power. With nearly double the frequency, along with double the cores, it is easy to tell how they arrived at over 4x the calculation power versus the older 21489. As such, they are potent, and I cannot wait for them to become mainstream.

2) I really want the ASRC, as having that on the fly is the most user friendly way to implement it.

And that is good to know on the variant. I haven't dove into the schematics as much yet (playing catch up now that I have this information at hand.

3) Yes, I personally do not want 5.1 through SPDIF, but I did like that this is an option (even if I don't want it). As to you doing the mainboard with the processor, you are right. All are digital at that point. But, I was meaning the backplane and DAC/ADCs that you can buy with their product, which has 4 analog input on it. The way those are supposed to be wired to the processor is to have the analog first in the list of inputs, then the digital inputs. But, that is still dependent on the manufacturer implementing the tracings in that way. And I have not compared the schematics to the ADSP-21489 data sheet yet.

As to the SPORTs, I saw at least one mention using those to create external controls connected to potentiometers. Something to keep in mind.

Regarding ASRC on one and not the other input, it most likely would be applied to all signals with passthrough if the rates match that of the device. But it should be lego like, which is how they have made sigmastudio for batches of code. You could optimize coding if doing from scratch instead of code batches that get plugged in, but that is a different conversation.

5. as to that, once I get it done, pictures will be shared! As to icepower, ONLY buy their new 300A2 or 400A2. Both have good properties on low distortion. The rest are not that great. I got the 3EAudio https://www.3e-audio.com/amplifier-kits/tpa3255-2ch-260w/

I cannot find the original design now, but those are $165 each. But there are numerous designs that are noteworthy with the TPA3255.

6. Yep, why I mentioned it. When I tested how many taps it allows with 2.10 and 2.11, and then double checked the engine of the compiler being updated, it has to be more efficient compiling that allows for more instructions.

https://www.digchip.com/datasheets/8831595-adsp-21489-high-performance.html

and

'5.4GFLOPs, 1.8GMACS Floating-pt SHARC+ DSP performance (2x 450MHz)' for sc57x/2157x

https://www.analog.com/en/products/landing-pages/001/adsp-sc57x-2157x-family.html

so it seems there is 2x difference in peak number of operations between sharc and sharc+ cores at same frequency.. well at least on paper

I was looking for real use case benchmark.. best if someone had both chips and put FIR filters to the max.. then we could be sure about performance difference in our use case.

Its getting more complicated when we look at FIR Accelerators:

SHARC core

The FIR (finite impulse response) accelerator consists of a 1024

word coefficient memory, a 1024 word deep delay line for the

data, and four MAC units. A controller manages the accelerator.

The FIR accelerator runs at the peripheral clock frequency.

SHARC+ core

The finite impulse response (FIR) accelerator consists of a

1024 word coefficient memory, a 1024 word deep delay line for

the data, and four MAC units. A controller manages the acceler-

ator. The FIR accelerator runs at the peripheral clock frequency.

The FIR accelerator can access all memory spaces and can run

concurrently with the other accelerators on the processor.

====

Seems like same thing... at first look only frequency should matter

but there is more

sharc+ has L2 cache, and much faster memory DDR3

while sharc is on SDR... can it cause bottleneck?

or if we use FIR filtering only and we have sharc and sharc+ core at same frequency using fir accelerator it will have same speed on both chips?

-----------------------------------------------

Now what I see more interesting part IIR:

SHARC core

The IIR (infinite impulse response) accelerator consists of a

1440 word coefficient memory for storage of biquad coeffi-

cients, a data memory for storing the intermediate data, and one

MAC unit. A controller manages the accelerator. The IIR accel-

erator runs at the peripheral clock frequency.

SHARC+ core

The infinite impulse response (IIR) accelerator consists of a

1440 word coefficient memory for storage of biquad coeffi-

cients, a data memory for storing the intermediate data, and one

MAC unit. A controller manages the accelerator. The IIR accel-

erator runs at the peripheral clock frequency. The IIR

accelerator can access all memory spaces and run concurrently

with the other accelerators on the processor.

====

accelerator can access all memory spaces and run concurrently

with the other accelerators on the processor. --- okay.. so it looks like on

* on sharc core we can use either IIR accelerator or FIR accelerator, only one at a time

*on sharc+ core can use both IIR AND FIR accelerators same time.

---------------------------------------------

Can this be reason for 2x performance? Could be I guess

On other hand if that is true, and you want to fully load DSP with both FIR and IIR .. it will can be twice as fast just by this change in architecture.

Or can be same speed if you use only FIR or only IIR.. THEORETICALLY

Performance they put 5.4GFLOPs, 1.8GMACS is theoretical peak performance as I see, no bottlenecks and you use all the operations you can use simultaneously, even if there is no reason or real use case.

So sharc+ not twice as fast as sharc core? No idea.. maybe its even 6 times faster or more in some use case.. remember DDR3 vs SDR memory.. and no L2 cache on sharc core.. will it be bottle neck?

I just say companies like to mix Marketing, putting numbers in best way they can and mixing marketing with technical data.

To be sure we need a benchmark done on both chips.

I did an experiment with ADSP-21489 on how to use a single line in Sigma Studio for FIR filters.

One position "Single Precesion" and the second "Extended Precesion"

In fact, there is no difference. Neither delays for acoustics, nor the load on the DSP.

Regarding FIR filters, another video with a link to Github https://github.com/DeepSOIC/fir_crossover_design

Might be interesting

One position "Single Precesion" and the second "Extended Precesion"

In fact, there is no difference. Neither delays for acoustics, nor the load on the DSP.

Regarding FIR filters, another video with a link to Github https://github.com/DeepSOIC/fir_crossover_design

Might be interesting

For IPS, L2 size (thereby reducing memory calls) and faster memory (meaning faster movement of data through the memory to the cores) can have significant impact. DDR vs SDR is significantly faster. Unfortunately, we only get bits and pieces on what the instructions are. For example, the Million Multiply Accumulate Instructions per Second is one. Flops is another measure of a type of instruction. And performance can be effected on the basis of instruction (different instruction, different delta in performance gain). So on one measure there is 4x performance, others is double. But agreed that statements like that should be couched in dependent upon instruction set.1. Okay, didnt see this chart, I only found that 'The ADSP-21489 offers the highest performance – 450 MHz / 2700 MFLOPs'

https://www.digchip.com/datasheets/8831595-adsp-21489-high-performance.html

and

'5.4GFLOPs, 1.8GMACS Floating-pt SHARC+ DSP performance (2x 450MHz)' for sc57x/2157x

https://www.analog.com/en/products/landing-pages/001/adsp-sc57x-2157x-family.html

so it seems there is 2x difference in peak number of operations between sharc and sharc+ cores at same frequency.. well at least on paper

I was looking for real use case benchmark.. best if someone had both chips and put FIR filters to the max.. then we could be sure about performance difference in our use case.

Its getting more complicated when we look at FIR Accelerators:

SHARC core

The FIR (finite impulse response) accelerator consists of a 1024

word coefficient memory, a 1024 word deep delay line for the

data, and four MAC units. A controller manages the accelerator.

The FIR accelerator runs at the peripheral clock frequency.

SHARC+ core

The finite impulse response (FIR) accelerator consists of a

1024 word coefficient memory, a 1024 word deep delay line for

the data, and four MAC units. A controller manages the acceler-

ator. The FIR accelerator runs at the peripheral clock frequency.

The FIR accelerator can access all memory spaces and can run

concurrently with the other accelerators on the processor.

====

Seems like same thing... at first look only frequency should matter

but there is more

sharc+ has L2 cache, and much faster memory DDR3

while sharc is on SDR... can it cause bottleneck?

or if we use FIR filtering only and we have sharc and sharc+ core at same frequency using fir accelerator it will have same speed on both chips?

-----------------------------------------------

Now what I see more interesting part IIR:

SHARC core

The IIR (infinite impulse response) accelerator consists of a

1440 word coefficient memory for storage of biquad coeffi-

cients, a data memory for storing the intermediate data, and one

MAC unit. A controller manages the accelerator. The IIR accel-

erator runs at the peripheral clock frequency.

SHARC+ core

The infinite impulse response (IIR) accelerator consists of a

1440 word coefficient memory for storage of biquad coeffi-

cients, a data memory for storing the intermediate data, and one

MAC unit. A controller manages the accelerator. The IIR accel-

erator runs at the peripheral clock frequency. The IIR

accelerator can access all memory spaces and run concurrently

with the other accelerators on the processor.

====

accelerator can access all memory spaces and run concurrently

with the other accelerators on the processor. --- okay.. so it looks like on

* on sharc core we can use either IIR accelerator or FIR accelerator, only one at a time

*on sharc+ core can use both IIR AND FIR accelerators same time.

---------------------------------------------

Can this be reason for 2x performance? Could be I guess(good example would be DIRAC implementation as you mentioned)

On other hand if that is true, and you want to fully load DSP with both FIR and IIR .. it will can be twice as fast just by this change in architecture.

Or can be same speed if you use only FIR or only IIR.. THEORETICALLY

Performance they put 5.4GFLOPs, 1.8GMACS is theoretical peak performance as I see, no bottlenecks and you use all the operations you can use simultaneously, even if there is no reason or real use case.

So sharc+ not twice as fast as sharc core? No idea.. maybe its even 6 times faster or more in some use case.. remember DDR3 vs SDR memory.. and no L2 cache on sharc core.. will it be bottle neck?

I just say companies like to mix Marketing, putting numbers in best way they can and mixing marketing with technical data.

To be sure we need a benchmark done on both chips.

Also, remember that the 21489 is over a decade old. So doubling to quadroupling should, in theory, be easy. The ARM cores have the SIMD accelerator which allow for certain benefits. FIR accelerators benefit from SIMD and from the FIR accelerators. So I agree, we need more information and need someone to do comparative analysis. But I do not have all that information at hand (want to buy me toys?).

Yeah, I mentioned after that when I reset the memory settings to match the video, that is when it reduced the number of taps to 4,300 for me. So the memory settings are drastically limiting what it can support. Sorry about that, that was my bad. I did notice a difference when I set the schematic tab at first, before going to block schematic, which made no difference in block schematic. I hoped it was a weird software thing. But I was wrong, it is memory limitations.I did an experiment with ADSP-21489 on how to use a single line in Sigma Studio for FIR filters.

One position "Single Precesion" and the second "Extended Precesion"

In fact, there is no difference. Neither delays for acoustics, nor the load on the DSP.

View attachment 1067430

Regarding FIR filters, another video with a link to Github https://github.com/DeepSOIC/fir_crossover_design

Might be interesting

Meanwhile, if anyone has the flashing program for the newer boards using 3.5mm plugs, I need that software. The vendors I bought from never gave me the stuff to allow use of sigmastudio. I tried it from the video drop, but that won't even ask what file to load for mcu.

Sure they could make much stronger DPS... what lithography is 5th gen sharc.. maybe 28nm at best.. just changing process + adding transistors/multiplying compute units it would be huge jump... but does it make sense for Analog from economical point of view?For IPS, L2 size (thereby reducing memory calls) and faster memory (meaning faster movement of data through the memory to the cores) can have significant impact. DDR vs SDR is significantly faster. Unfortunately, we only get bits and pieces on what the instructions are. For example, the Million Multiply Accumulate Instructions per Second is one. Flops is another measure of a type of instruction. And performance can be effected on the basis of instruction (different instruction, different delta in performance gain). So on one measure there is 4x performance, others is double. But agreed that statements like that should be couched in dependent upon instruction set.

Also, remember that the 21489 is over a decade old. So doubling to quadroupling should, in theory, be easy. The ARM cores have the SIMD accelerator which allow for certain benefits. FIR accelerators benefit from SIMD and from the FIR accelerators. So I agree, we need more information and need someone to do comparative analysis. But I do not have all that information at hand (want to buy me toys?).

Yeah, I mentioned after that when I reset the memory settings to match the video, that is when it reduced the number of taps to 4,300 for me. So the memory settings are drastically limiting what it can support. Sorry about that, that was my bad. I did notice a difference when I set the schematic tab at first, before going to block schematic, which made no difference in block schematic. I hoped it was a weird software thing. But I was wrong, it is memory limitations.

Meanwhile, if anyone has the flashing program for the newer boards using 3.5mm plugs, I need that software. The vendors I bought from never gave me the stuff to allow use of sigmastudio. I tried it from the video drop, but that won't even ask what file to load for mcu.

Maybe some bug that you cant flash it. Do you have USBi disconnected? Think we all have same package of software. It shouldnt matter which mainboard you have there is nothing interesting there just i2s/spdif lines to DSP board. Unless you have some different revision of dsp board but I doubt.. you can post photos so I check with mine

I opened it and click on it and nothing. I wonder if it is me gutting Windows ISO that something is interfering with it. It is odd because I don't have usbi connected, I have tried it on two different systems (with and without a USB hub), after reboots, etc. It connects by microusb for control by the software, but it does not work for this program.

- Home

- Source & Line

- Digital Line Level

- Cheap ADSP21489 + 4in / 6out PCM1798 board