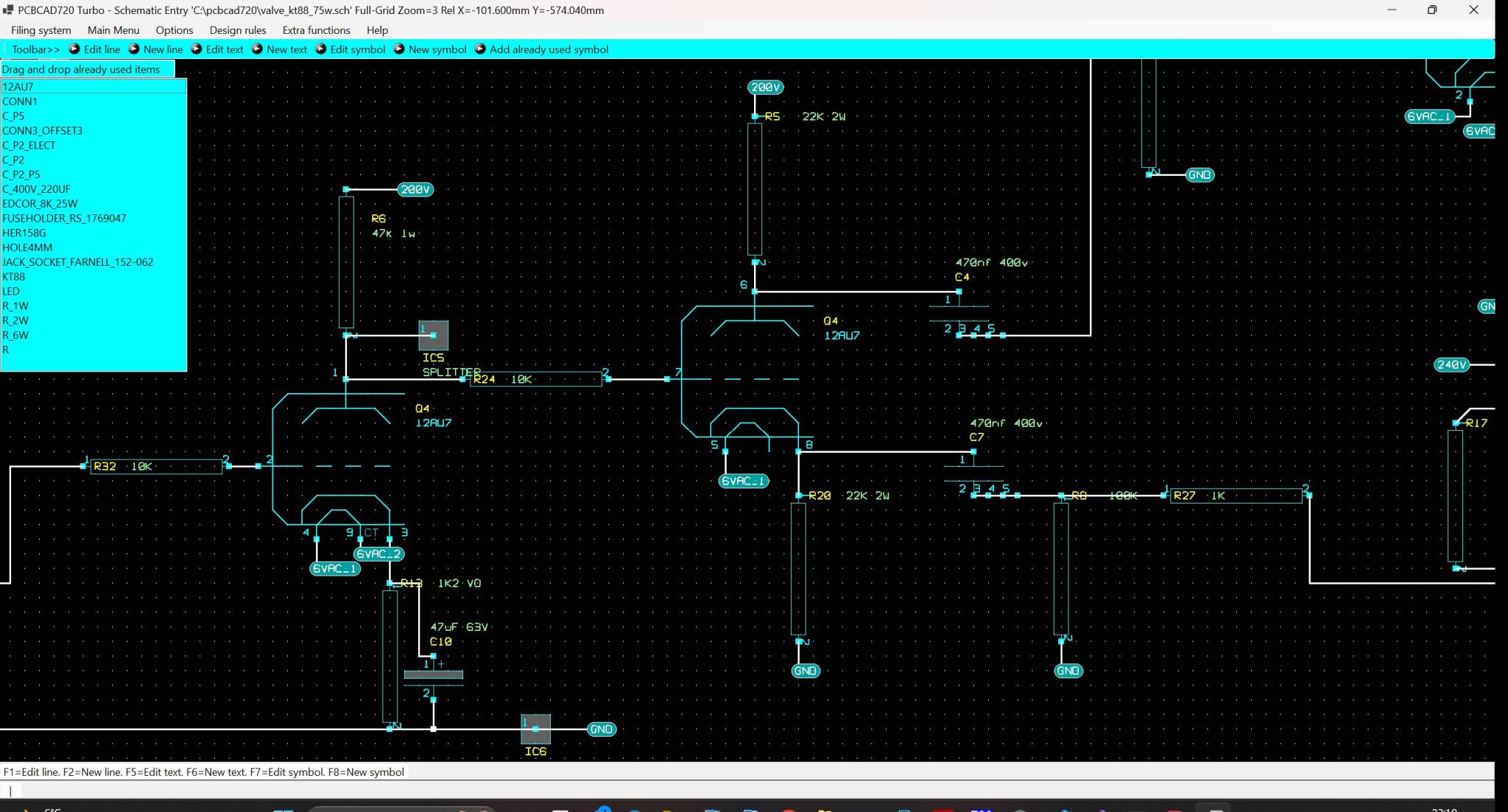

Started with LTSpice basically today on OSX. Drew up my first schematic, based on some reverse engineering of a tube amp I built yeears ago.

Entered the first stage, the phase splitter. Ran a simulation (.tran) with a 200Hz input @ 25 mV. Was expecting to see 2 signals 180 degrees out of phase on the outputs. But the simulation shows the both outputs in phase.

As this is a cathodyne circuit that would be impossible, and o'scope measurements confirm I get 2 inverted signals out. So I must be doing something wrong in LTSpice, but cant figure out what. ASC attached.

This is the sub file I'm using:

I also loaded the schematic in LTSpice in a windows VM , but result was the same.

Any hints appreciated.

Entered the first stage, the phase splitter. Ran a simulation (.tran) with a 200Hz input @ 25 mV. Was expecting to see 2 signals 180 degrees out of phase on the outputs. But the simulation shows the both outputs in phase.

As this is a cathodyne circuit that would be impossible, and o'scope measurements confirm I get 2 inverted signals out. So I must be doing something wrong in LTSpice, but cant figure out what. ASC attached.

This is the sub file I'm using:

*

* Generic triode model: 12AX7

* Copyright 2003--2008 by Ayumi Nakabayashi, All rights reserved.

* Version 3.10, Generated on Sat Mar 8 22:41:09 2008

* Plate

* | Grid

* | | Cathode

* | | |

.SUBCKT 12AX7 A G K

BGG GG 0 V=V(G,K)+0.59836683

BM1 M1 0 V=(0.0017172334*(URAMP(V(A,K))+1e-10)) ** -0.2685074

BM2 M2 0 V=(0.84817287*(URAMP(V(GG)+URAMP(V(A,K))/88.413802)+1e-10)) ** 1.7685074

BP P 0 V=0.001130216*(URAMP(V(GG)+URAMP(V(A,K))/104.24031)+1e-10) ** 1.5

BIK IK 0 V=U(V(GG))*V(P)+(1-U(V(GG)))*0.00071211506*V(M1)*V(M2)

BIG IG 0 V=0.000565108*URAMP(V(G,K)) ** 1.5*(URAMP(V(G,K))/(URAMP(V(A,K))+URAMP(V(G,K)))*1.2+0.4)

BIAK A K I=URAMP(V(IK,IG)-URAMP(V(IK,IG)-(0.00058141055*URAMP(V(A,K)) ** 1.5)))+1e-10*V(A,K)

BIGK G K I=V(IG)

* CAPS

CGA G A 1.7p

CGK G K 1.6p

CAK A K 0.5p

.ENDS

I also loaded the schematic in LTSpice in a windows VM , but result was the same.

Any hints appreciated.

Attachments

Another schematic I tested had biasing with the same result. But with or without biasing, anode and cathode voltage should not be in phase, right?

And the physical circuit (not a simulation) does have 2 outputs with 180 degree phase shift..

And the physical circuit (not a simulation) does have 2 outputs with 180 degree phase shift..

The biggest problem is that the plate voltage on the first tube is too high, so the phase splitter is saturated. The phase splitter cathode needs to be 1/4 the supply voltage (280/4=70) and the plate at 3/4 (280*3/4=210). And If you are going to drop the supply with the 33k, it needs a filter cap. A quick solution is to use 1200K for the first plate resistor. You could also reduce the cathode resistor.

Attachments

Here's a working circuit.

I cheated and used previous stage anode voltage to set phase splitter voltages.

I cheated and used previous stage anode voltage to set phase splitter voltages.

The cathode resistor R2 would be 390 Ohms. This is probably a better solution.The biggest problem is that the plate voltage on the first tube is too high, so the phase splitter is saturated. The phase splitter cathode needs to be 1/4 the supply voltage (280/4=70) and the plate at 3/4 (280*3/4=210). And If you are going to drop the supply with the 33k, it needs a filter cap. A quick solution is to use 1200K for the first plate resistor. You could also reduce the cathode resistor.

Thanks Steve!

Ahum... So why does the simulation fail and the actual circuit work. I used an old diagram as a start for reverse engineering. That diagram used a paraphase with 12AX7. So at one point (wind back 30 years) I changed that to a cathodyne, but I also changed the tube to a JAN6189W. And I failed to check the tube, assuming it was still a 12AX7. Why am I reverse engineering my own amp? It was all on my PC at the time, and the tape backup can't be restored anymore. All I have is a single sheet of paper, which turns out to be not the latest design. But I do have three caps of different types behind the 33k resistor (100uF Electrolytical, a 10uF MKP and a 0.1uF MKS)

From Steve's comments I see that even with a 6189W (==12AU7) the circuit can be improved by dropping the U1 cathode resistor to approx 3k to obtain the 1/4 cathode- 3/4 anode voltage split in the phase splitter?

The outputs can be matched by using a bias circuit and fiddling a bit with R3 I guess?

Ahum... So why does the simulation fail and the actual circuit work. I used an old diagram as a start for reverse engineering. That diagram used a paraphase with 12AX7. So at one point (wind back 30 years) I changed that to a cathodyne, but I also changed the tube to a JAN6189W. And I failed to check the tube, assuming it was still a 12AX7. Why am I reverse engineering my own amp? It was all on my PC at the time, and the tape backup can't be restored anymore. All I have is a single sheet of paper, which turns out to be not the latest design. But I do have three caps of different types behind the 33k resistor (100uF Electrolytical, a 10uF MKP and a 0.1uF MKS)

From Steve's comments I see that even with a 6189W (==12AU7) the circuit can be improved by dropping the U1 cathode resistor to approx 3k to obtain the 1/4 cathode- 3/4 anode voltage split in the phase splitter?

The outputs can be matched by using a bias circuit and fiddling a bit with R3 I guess?

Last edited:

Thanks Lyda for your view reference bias circuit. But like Nigels post, the bias is provided by the previous stage. There is no capacitor coupling at the input. That lacking capacitor indeed causes what Steve was stating, the first stage affects the dc setup of the second stage. Which is perhaps bad, but it also cuts out another cap in the signal path, which is good 🙂. So for the time being I'm going to leave it without a cap, unless things become unstable.

- Home

- Design & Build

- Software Tools

- Newbee question on LTSpice