Attachments

And results next to each other:

Non-inverted | Inverted | Voltage follower

OPA2134 - 0.00671% | 0.000006668% | 0.00668%

NE5532 -- 0.000129% | 0.00000659% | 0.0000434%

LM4562 -- 0.00000703% | 0.00000569% | 0.00000611%

OPA1612 - 0.00000956% | 0.0000101% | 0.00000623%

OPA1656 - 0.00000657% | 0.0045749% | 0.00000686%

OPA1652 - 0.0002008% | 0.000267% | 0.0000244%

Non-inverted | Inverted | Voltage follower

OPA2134 - 0.00671% | 0.000006668% | 0.00668%

NE5532 -- 0.000129% | 0.00000659% | 0.0000434%

LM4562 -- 0.00000703% | 0.00000569% | 0.00000611%

OPA1612 - 0.00000956% | 0.0000101% | 0.00000623%

OPA1656 - 0.00000657% | 0.0045749% | 0.00000686%

OPA1652 - 0.0002008% | 0.000267% | 0.0000244%

Whats the mechanism behind such ringing with the 1nf caps? I recently did a discrete opamp layout and did end up spraying the decouplers everywhere thinking it was a good idea. They are at every power trace entry point at constant current sources and the output bjt source pin.

Two caps in parallel form a series RLC circuit with the values of R,L,C equal to the series combination of all corresponding elements.

Damping factor is R/2 sqrt( C/L ) and should be >1 to avoid ringing.

So circuits with low C and high L (traces) have lower damping, whereas circuits with low L (power/ground planes) make it much easier to have good damping.

For me, optimal conditions also means to have a decent assembly process. Take the proper precautions against ESD, don't overheat the OpAmp during assembly and properly clean the PCB when you are done soldering.

With regards to the SPICE simulations I recommend you properly read what Tom and steveu already said. If you want meaningful, comparative measurements, go here: http://www.nanovolt.ch/resources/ic_opamps/index.html

About 4-Layer boards:

My preferred 4-Layer stackup for small signal stuff looks slightly different than peufeu's, however it really comes down to what exactly you are building.

Layer 1: Main Signal Layer + Ground Pour

Layer 2: Ground plane

Layer 3: Split power plane

Layer 4: Auxiliary Signal Layer + Ground Pour

When only OpAmps are used and they are arranged somewhat neatly, a split power plane works quite well and you have more space for additional, less critical routing on the bottom layer. For other designs there might be very valid reasons to have separate power planes. If for example parts with high thermal dissipation are used you probably want an external plane or large pour connected to their thermal pads.

With regards to the SPICE simulations I recommend you properly read what Tom and steveu already said. If you want meaningful, comparative measurements, go here: http://www.nanovolt.ch/resources/ic_opamps/index.html

About 4-Layer boards:

My preferred 4-Layer stackup for small signal stuff looks slightly different than peufeu's, however it really comes down to what exactly you are building.

Layer 1: Main Signal Layer + Ground Pour

Layer 2: Ground plane

Layer 3: Split power plane

Layer 4: Auxiliary Signal Layer + Ground Pour

When only OpAmps are used and they are arranged somewhat neatly, a split power plane works quite well and you have more space for additional, less critical routing on the bottom layer. For other designs there might be very valid reasons to have separate power planes. If for example parts with high thermal dissipation are used you probably want an external plane or large pour connected to their thermal pads.

thanks. i see it. i did keep the return node of the caps close together (end to end?) along with ground plane so i think it should be okView attachment 1074532

Two caps in parallel form a series RLC circuit with the values of R,L,C equal to the series combination of all corresponding elements.

Damping factor is R/2 sqrt( C/L ) and should be >1 to avoid ringing.

So circuits with low C and high L (traces) have lower damping, whereas circuits with low L (power/ground planes) make it much easier to have good damping.

I think your post above is hyperbolic. Are you coming from the Pass forum, by chance???I would not equal best sound with lowest THD.

THD is just one of the metrics that are used to judge quality.

Personally I find running op-amps in class AB a bad idea since this inevitably creates crossover distortion and it is entirely up to GNFB to reduce this ugly kind of distortion, and GNFB becomes less effective in the higher frequency range.

Thus, running the op-amp in class A seems to be a really good idea.

It's not the 1970s anymore, you know. I ask you to show me one example of crossover distortion in a quality, modern op-amp intended for audio use.

Douglas Self has a section on output biasing of the 5532 in his book "The Design of Active Crossovers". I own the 2011 version, and the section (13.10) is found starting on page 389. Here is a quote:

In power amplifiers the main aim is to prevent the output stage from traversing the crossover region at low powers. In the 5532 at least the crossover region is not easy to spot on the distortion residual, the general effect being of second and third harmonic distortion rather than spikes or edges; it appears the 5532 output stage is more linear when it is pulling down rather than pulling up, and the biasing current is compensating for this.

You can then inspect Figure 13.12 to see an example of the "dramatic" impact that biasing has on the distortion level. It falls from about 0.0045% to 0.0035% at 1kHz. This is really not much of an improvement. Self has to resort to using the worst configuration and a gain of 14 times (that is pretty high gain for a single-stage 5532) to get better results from biasing (see Figure 13.13) where he shows that for the series feedback configuration he could achieve a distortion reduction from about 0.0012% to 0.0004%. Neither of these figures is going to be "ugly" at the crossover point with or without biasing, it just reduces the overall distortion for this op-amp in some cases.

Keep in mind we are not talking about a power amp here. This is small signal integrated. The fact that Self mentions that there are no significant crossover glitches should show that this is just not really an issue for a modern op-amp, although I do not have actual plots of this for any op-amp, possibly because it is not all that measurable. Self even mentions that trying to bias the output of the 5532 is "clumsy" (his words) when you can "just use a more linear op-amp like the LM4562". This seems to be Self admitting that there are even better op-amps today than the 5532 (which is correct), meaning that the crossover distortion would be even less concerning for them.

If you feel differently, please show me some compelling evidence to support your argument.

Yeah I agree with you...If you feel differently, please show me some compelling evidence to support your argument.

First, the small signal output transistors in an opamp are going to be much faster than power devices, so unless it's a crummy old opamp, I don't think you'll find the usual crossover spikes due to slow turn-off, charge storage, and junction capacitance.

First and a half, they're not using crummy slow drivers like MJE15030 in these chips. You can expect the driver to be very fast.

Second, consider an opamp with an idle output stage bias current of 2mA, that is being asked to swing +/-5mA. That's pretty realistic, 5V peak into 1k... it's already a bit of heavy lifting for an opamp... It will go into class B, but it's only outputting 2.5x its bias current. Now consider a power amp biased at 50mA, which is already a lot, and this time it is outputting a realistic loudspeaker current of say +/-500mA. So it's outputting 10x its bias current. 20x, if it was biased at 25mA.

In this example, the power amp must traverse its entire crossover region 4 times faster than the opamp, with devices that are at least 10x slower, with maybe 100x more capacitance, and it probably has lower open loop gain too.

If you want to check crossover distortion in your opamp:

- Make it output something like 20kHz, 1V into 1kOhm

- Add a DC offset and sweep it

With zero DC offset, the opamp will be in class A. With a large DC offset, it will be in pure class B, only one output transistor will be on. When DC offset is adjusted to center the point when one transistor turns off on the middle of your sinewave, this is the maximum distortion point if it has gm-doubling, because this puts the highest slew rate point of the signal on the worst part of the transfer function (the point where gm doubles and makes a step). If it doesn't have gm-doubling but the output stage is kinda underbiased, gm is like a V curve, and the maximum distortion point is with a small DC offset to center the sinewave almost but not quite on the bottom of the "V". Or you could just sweep the DC and measure the distortion, and take the worst case value.

You do realize, and I assume you understood, as explained by Tom, that these are behavioral models only which do not simulate the exact internals, and thus the distortion result may be right, or maybe not.I discovered how to simulate distortion using TINA TI 🤓

I wouldn't base a design decision on it.

Jan

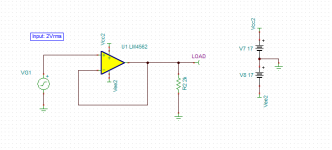

You are forgetting to add the feedback network as part of the load. The load for the circuits in posts #39 and #40 is actually 1.2k.Here are results for inverting amp:

View attachment 1074528

Inverting amp

Frequency = 1KHz

Input voltage = 2Vrms

Gain = 3, Feedback resistor = 3K, Input resistor = 1K

Load = 2K

Time measurment = 1.75mS, at peak voltage of 8.43V

OPA2134 - 0.000006668%

NE5532 -- 0.00000659%

LM4562 -- 0.00000569%

OPA1612 - 0.0000101%

OPA1656 - 0.0045749%

OPA1652 - 0.000267%

Mike

This is what is modeled in, for instance, the OPAx134 types:

*****************************************************************************

Note that distortion is not mentioned. Which makes sense because modeling that would require a model that is the same as the real chip.

This is what it says on the LM4562 model:

* Model Version: 1.1

*

*****************************************************************************

*

* Updates:

*

*****************************************************************************

XD4 VSS 5 IDEAL_DIODE

+PARAMS: EMCO = 0.01 BRKV = 60 IBRKV = 0.001

XD3 5 VDD IDEAL_DIODE

+PARAMS: EMCO = 0.01 BRKV = 60 IBRKV = 0.001

XD2 VSS 6 IDEAL_DIODE

+PARAMS: EMCO = 0.01 BRKV = 60 IBRKV = 0.001

XD1 6 VDD IDEAL_DIODE

+PARAMS: EMCO = 0.01 BRKV = 60 IBRKV = 0.001

ALWAYS check your models to see that they allow you to simulate what you need.

Otherwise it's a waste of time, or worse, putting you on the wrong foot.

Jan

*****************************************************************************

- Model Usage Notes:

- 1. The following parameters are modeled:

- a. OPEN-LOOP GAIN AND PHASE VS. FREQUENCY WITH RL, CL EFFECTS (Aol)

- b. UNITY GAIN BANDWIDTH (GBW)

- c. INPUT COMMON-MODE REJECTION RATIO VS. FREQUENCY (CMRR)

- d. POWER SUPPLY REJECTION RATIO VS. FREQUENCY (PSRR)

- e. DIFFERENTIAL INPUT IMPEDANCE (Zid)

- f. COMMON-MODE INPUT IMPEDANCE (Zic)

- g. OPEN-LOOP OUTPUT IMPEDANCE VS. FREQUENCY (Zo)

- h. OUTPUT CURRENT THROUGH THE SUPPLY (Iout)

- i. INPUT VOLTAGE NOISE DENSITY VS. FREQUENCY (en)

- j. INPUT CURRENT NOISE DENSITY VS. FREQUENCY (in)

- k. OUTPUT VOLTAGE SWING vs. OUTPUT CURRENT (Vo)

- l. SHORT-CIRCUIT OUTPUT CURRENT (Isc)

- m. QUIESCENT CURRENT (Iq)

- n. SETTLING TIME VS. CAPACITIVE LOAD (ts)

- o. SLEW RATE (SR)

- p. SMALL SIGNAL OVERSHOOT VS. CAPACITIVE LOAD

- q. LARGE SIGNAL RESPONSE

- r. OVERLOAD RECOVERY TIME (tor)

- s. INPUT BIAS CURRENT (Ib)

- t. INPUT OFFSET CURRENT (Ios)

- u. INPUT OFFSET VOLTAGE (Vos)

- v. INPUT OFFSET VOLTAGE VS. TEMPERATURE (Vos Drift)

- w. INPUT COMMON-MODE VOLTAGE RANGE (Vcm)

- x. INPUT OFFSET VOLTAGE VS. INPUT COMMON-MODE VOLTAGE (Vos vs. Vcm)

- y. INPUT/OUTPUT ESD CELLS (ESDin, ESDout)

Note that distortion is not mentioned. Which makes sense because modeling that would require a model that is the same as the real chip.

This is what it says on the LM4562 model:

* Model Version: 1.1

*

*****************************************************************************

*

* Updates:

*

- Version 1.0 : Release to Web

- Version 1.1 : a. Adjust Input Bias Current

- b. Adjust input current white noise

- c. Adjust common mode input range

*****************************************************************************

- Notes:

- The following are the model parameters being modeled:

- Voltage Noise, Current Noise, PSRR, CMRR, Aol, GBW, Slew Rate,

- Output Voltage Swing, Ishort Circuit, Commond Mode Input Range,

- Input bias current, input bias offset, voltage offset and quiescent

- current

XD4 VSS 5 IDEAL_DIODE

+PARAMS: EMCO = 0.01 BRKV = 60 IBRKV = 0.001

XD3 5 VDD IDEAL_DIODE

+PARAMS: EMCO = 0.01 BRKV = 60 IBRKV = 0.001

XD2 VSS 6 IDEAL_DIODE

+PARAMS: EMCO = 0.01 BRKV = 60 IBRKV = 0.001

XD1 6 VDD IDEAL_DIODE

+PARAMS: EMCO = 0.01 BRKV = 60 IBRKV = 0.001

ALWAYS check your models to see that they allow you to simulate what you need.

Otherwise it's a waste of time, or worse, putting you on the wrong foot.

Jan

Last edited:

I don't use TINA but this is the OPA2132 model for microcap:

.SUBCKT OPA2132_BB 1 2 3 4 5

*

C1 11 12 3.240E-12

C2 6 7 8.000E-12

CSS 10 99 1.000E-30

DC 5 53 DX

DE 54 5 DX

DLP 90 91 DX

DLN 92 90 DX

DP 4 3 DX

EGND 99 0 POLY(2) (3,0) (4,0) 0 .5 .5

FB 7 99 POLY(5) VB VC VE VLP VLN 0 248.0E6 -250E6 250E6 250E6 -250E6

GA 6 0 11 12 402.0E-6

GCM 0 6 10 99 4.020E-9

ISS 3 10 DC 160.0E-6

HLIM 90 0 VLIM 1E3

J1 11 2 10 JX

J2 12 1 10 JX

R2 6 9 100.0E3

RD1 4 11 2.490E3

RD2 4 12 2.490E3

RO1 8 5 20

RO2 7 99 20

RP 3 4 7.500E3

RSS 10 99 1.250E6

VB 9 0 DC 0

VC 3 53 DC 1.200

VE 54 4 DC .9

VLIM 7 8 DC 0

VLP 91 0 DC 40

VLN 0 92 DC 40

.MODEL DX D(IS=800.0E-18)

.MODEL JX PJF(IS=2.500E-15 BETA=1.010E-3 VTO=-1)

.ENDS

The only active devices are the two input JFETs, plus 2 diodes, all the rest is dependent sources and polynomials. There are G's and caps for the open loop gain. This is not going to produce anything resembling real life THD.

.SUBCKT OPA2132_BB 1 2 3 4 5

*

C1 11 12 3.240E-12

C2 6 7 8.000E-12

CSS 10 99 1.000E-30

DC 5 53 DX

DE 54 5 DX

DLP 90 91 DX

DLN 92 90 DX

DP 4 3 DX

EGND 99 0 POLY(2) (3,0) (4,0) 0 .5 .5

FB 7 99 POLY(5) VB VC VE VLP VLN 0 248.0E6 -250E6 250E6 250E6 -250E6

GA 6 0 11 12 402.0E-6

GCM 0 6 10 99 4.020E-9

ISS 3 10 DC 160.0E-6

HLIM 90 0 VLIM 1E3

J1 11 2 10 JX

J2 12 1 10 JX

R2 6 9 100.0E3

RD1 4 11 2.490E3

RD2 4 12 2.490E3

RO1 8 5 20

RO2 7 99 20

RP 3 4 7.500E3

RSS 10 99 1.250E6

VB 9 0 DC 0

VC 3 53 DC 1.200

VE 54 4 DC .9

VLIM 7 8 DC 0

VLP 91 0 DC 40

VLN 0 92 DC 40

.MODEL DX D(IS=800.0E-18)

.MODEL JX PJF(IS=2.500E-15 BETA=1.010E-3 VTO=-1)

.ENDS

The only active devices are the two input JFETs, plus 2 diodes, all the rest is dependent sources and polynomials. There are G's and caps for the open loop gain. This is not going to produce anything resembling real life THD.

Jan beat me to it. Distortion is not commonly included in the model. SPICE will happily give you a THD number, but it's not rooted in reality unless the model includes distortion.

Also be careful when simulating ultra-low distortion. A slight change in the step size can really throw off the FFT math and give you THD figures that are out in the weeds. Always ensure that you have at least the same number of points in your simulation as you have points in the FFT.

I will often simulate THD even if it's not included in the model. That's just a simple sanity check so see if the circuit is fundamentally broken. If the simulation says the circuit has, say, 1-2 % THD I look around to see if I can figure out why. But if it says 0.00x % THD and the rest of my sims look good, I conclude that the circuit could be worth prototyping.

Tom

Also be careful when simulating ultra-low distortion. A slight change in the step size can really throw off the FFT math and give you THD figures that are out in the weeds. Always ensure that you have at least the same number of points in your simulation as you have points in the FFT.

I will often simulate THD even if it's not included in the model. That's just a simple sanity check so see if the circuit is fundamentally broken. If the simulation says the circuit has, say, 1-2 % THD I look around to see if I can figure out why. But if it says 0.00x % THD and the rest of my sims look good, I conclude that the circuit could be worth prototyping.

Tom

I think your post above is hyperbolic. Are you coming from the Pass forum, by chance???

It's not the 1970s anymore, you know. I ask you to show me one example of crossover distortion in a quality, modern op-amp intended for audio use.

Douglas Self has a section on output biasing of the 5532 in his book "The Design of Active Crossovers". I own the 2011 version, and the section (13.10) is found starting on page 389. Here is a quote:

You can then inspect Figure 13.12 to see an example of the "dramatic" impact that biasing has on the distortion level. It falls from about 0.0045% to 0.0035% at 1kHz. This is really not much of an improvement. Self has to resort to using the worst configuration and a gain of 14 times (that is pretty high gain for a single-stage 5532) to get better results from biasing (see Figure 13.13) where he shows that for the series feedback configuration he could achieve a distortion reduction from about 0.0012% to 0.0004%. Neither of these figures is going to be "ugly" at the crossover point with or without biasing, it just reduces the overall distortion for this op-amp in some cases.

Keep in mind we are not talking about a power amp here. This is small signal integrated. The fact that Self mentions that there are no significant crossover glitches should show that this is just not really an issue for a modern op-amp, although I do not have actual plots of this for any op-amp, possibly because it is not all that measurable. Self even mentions that trying to bias the output of the 5532 is "clumsy" (his words) when you can "just use a more linear op-amp like the LM4562". This seems to be Self admitting that there are even better op-amps today than the 5532 (which is correct), meaning that the crossover distortion would be even less concerning for them.

If you feel differently, please show me some compelling evidence to support your argument.

Hyperbolic maybe - Pass fan certainly not.

First of all, thank you very much for mentioning Douglas Self's work here. I was not aware of his investigation and find it highly interesting. Unfortunately I don't own this book.

A reduction of the distortion from 0.0045% to 0.0035% is dramatic - this is 32%. From 0.0012% to 0.0004% is even 66%. I had not expected such an outcome. I don't understand why distortion gets so much better with class A biasing. This should only be effective to remove crossover distortion once the op-amp is driven out of its class A range. Would that mean that the difference is made up by crossover distortion then? I doubt this somehow because this would imply a lot of crossover distortion, which I would not expect.

My expectation was that class A biasing has side effects, maybe even increased distortion in turn to get rid of crossover distortion. And I would expect that crossover distortion in op-amps is not really significant, maybe not measurable at all. This is why I wrote THD should not be overestimated.

The harmonic profile is very important, too. In turn to get rid of higher order harmonics, I would sacrifice something like a bit higher h2 or h3.

I'm not talking about Pass amp THD levels here, BTW.

I don't have any better evidence than the evidence Douglas Self provided already. Self provides the best evidence I can imagine.

My main point is that I find it not a good idea to wrap a ton of GNFB around a circuit that is not very linear to begin with, like an amplifier in class AB operation. Wrapping a ton of GNFB around a more linear circuit, like an amplifier in class A operation, seems more promising to me. Of course an IC op-amp has a super tiny output stage not comparable with a huge power amplifier output stage, which allows very high ULGF and therefore good attenuation of distortion even at higher frequency, but still there is some significant non-linearity in the loop. Unlike with high power amplifiers, class A operation is feasible for small signal amplifiers in some applications so why bother with additional distortion added by class AB operation?

Did Self write anything about negative side effects of class A biasing?

The method to investigate this is the same as for a power amp.This should only be effective to remove crossover distortion once the op-amp is driven out of its class A range. Would that mean that the difference is made up by crossover distortion then? I doubt this somehow because this would imply a lot of crossover distortion, which I would not expect.

Optimal condition for OPA1642 to give best sound is simply to ask it politely to do so. Try it, it works.

I find the OPA1642 sounds much better when powered up than when not. From this experiment I conclude that powering the opamp is key to good sound. 😉

Tom

Tom

Most op amps used for audio have enough standing current in their output stages to be operating in class A with typical line level signals and output (including feedback) loading. They typically don’t drive 8 ohms, or even 800 so the current swings are small. Then there is no crossover distortion - like a high- biased Krell running at two watts. When you need/want to drive a lower impedance, or near the full 13 volt output swing, you may want to force it into class A. Until then it is probably unnecessary. Junkers like the LM358 can even be listenable with 2 mA of forced bias. That will do nothing for an OPA1642 or even 5532, but 20 might depending on what you’re doing with it. Downside of course is the dissipation. When I want to drive terminated cables, headphones, or transformers with limited primary inductance I’ll put an emitter follower inside the feedback and off-load all the extra dissipation to it because that current source will be more like 50-100 mA, and op amps by themselves won’t put that out anyway. When driving an SE follower, the op amp will always be sourcing, never sinking, so it’s forced to class A regardless.

- Home

- Amplifiers

- Chip Amps

- Optimal conditions for opamps to give best sound