Well , I think I finally understand the DR9001 datasheet , cant be more precise now 🙂

.

.

Last edited:

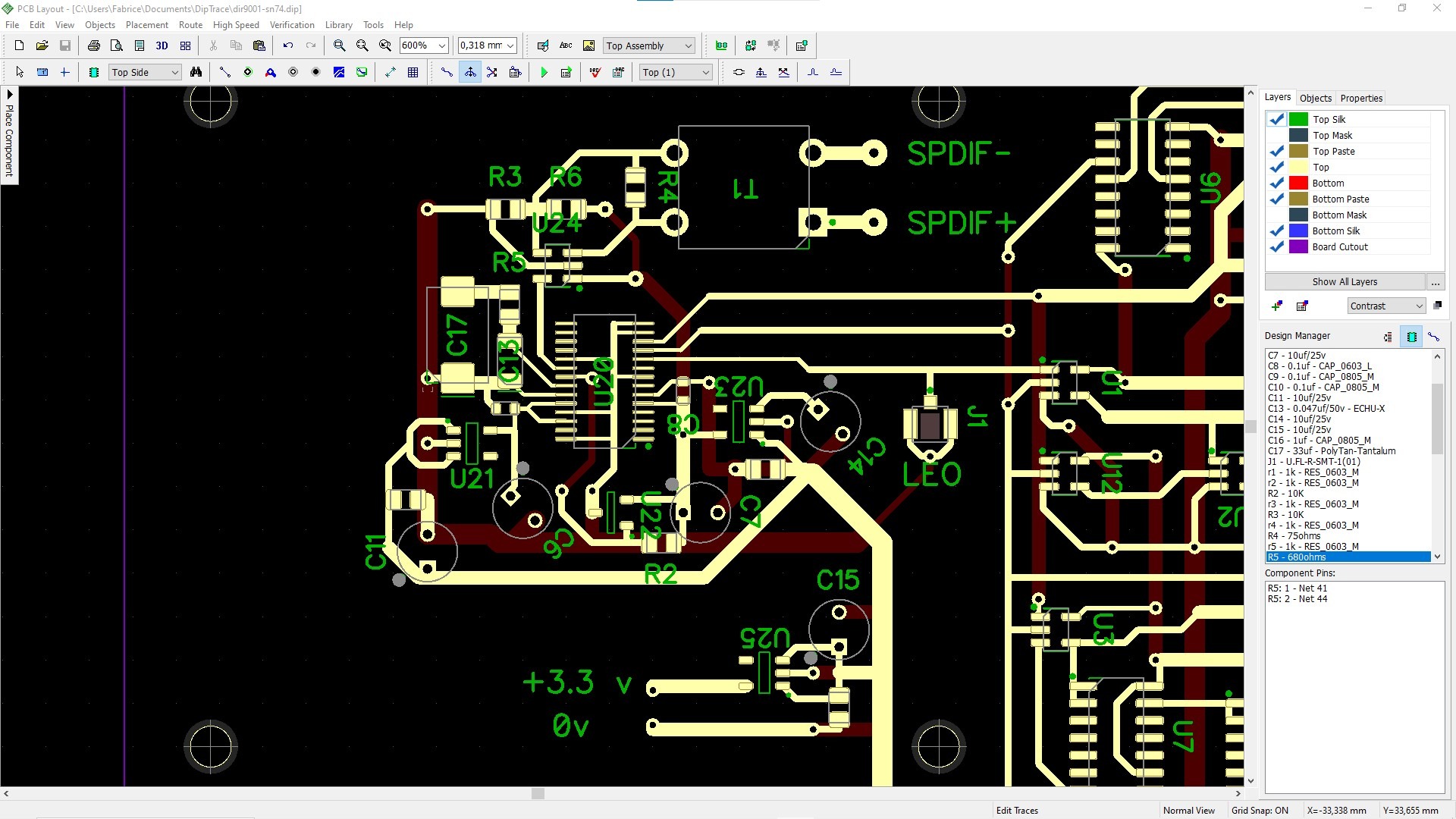

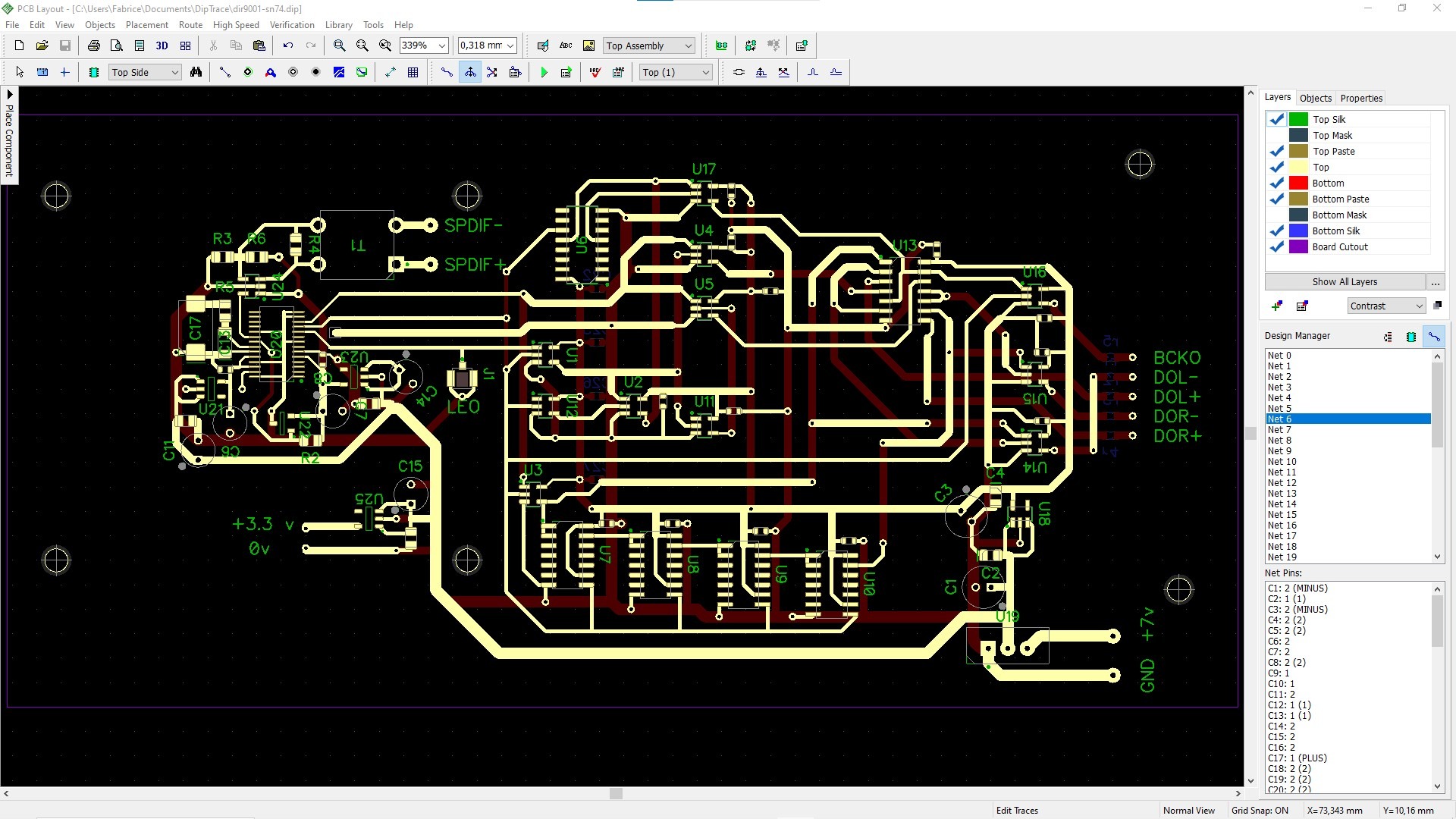

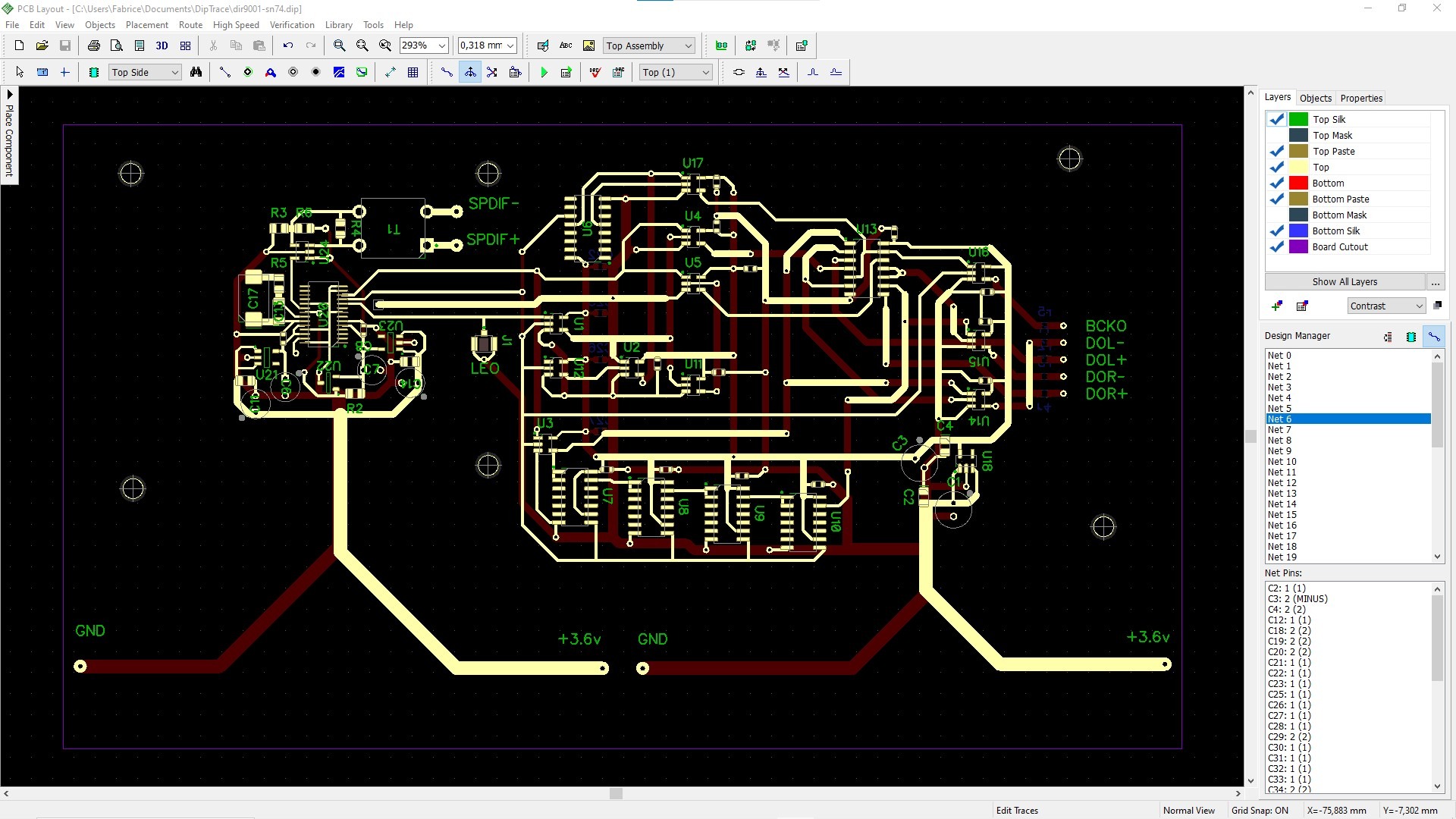

It seems to me that routing a pcb for the better it's like an never ending story , for the skilled one it will be much easier 😎

Hafter having read carefully the all data sheet of the all components , here is the " final " shot :

.

Hafter having read carefully the all data sheet of the all components , here is the " final " shot :

.

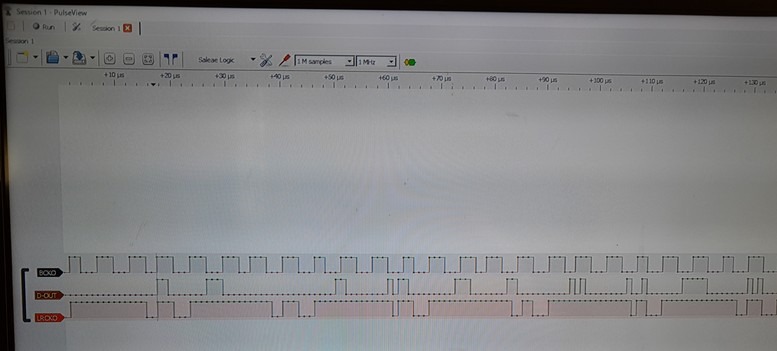

For those who wants to get deeper , the logic works at 2.5 v , and the protocol is Left justified , not I2S

.

.

@fabrice63, arrange the connection of the PLL filter components to ground a little more, DS is quite precise here. Panasonic ECHU is a good choice for SMD film or you can freely use COG.

Separate the power supply of the DIR9001 itself from the rest. Try that DIR9001 has its own secondary on the transformer. This is the difference between an ordinary and top-quality DAC, as well as the quality of the regulator.

Separate the power supply of the DIR9001 itself from the rest. Try that DIR9001 has its own secondary on the transformer. This is the difference between an ordinary and top-quality DAC, as well as the quality of the regulator.

Attachments

Thank you Grunf , will see what I can do 😉

it seems that they ugrade their datasheet , good to know !!

.

it seems that they ugrade their datasheet , good to know !!

.

Last edited:

Here are some hints, although most are for the DAC board and not this logic board..

-Limit input bandwith to below 10Mhz, it does not help you and increases ground bounce. We discussed it in the thread previously but here is article to help you. Actually there's more on that site, you should read all of them, in order, they're very good.

-If you do not use 50Hz reclock, DEM caps should absolutely be C0G, or film. Otherwise, low leakage like UKL's.

-Take extreme care of DEM capacitors return currents.

-Minimise loop length for all current return paths, loop inductance

-Decouple all ICs locally with smaller value ceramic cap that is close to the pin.

-The DGND should be connected only on place with the AGND pin right next to the input pins (pin 4 or 5 or something). Dont just do a whole copper pour and hope for the best, you can get good results this way also but only if your layout is good. Basically you can do two copper pours, one for digital and one for analog, and both should be connected in the area between these two pins on the DAC itself. But you must at the same time take care of DEM cap return currents, this necessitates 4 layers.

That is off the top of my head, there is more if you spend reading thread...but its enough to make a good dac for starters.

-Limit input bandwith to below 10Mhz, it does not help you and increases ground bounce. We discussed it in the thread previously but here is article to help you. Actually there's more on that site, you should read all of them, in order, they're very good.

-If you do not use 50Hz reclock, DEM caps should absolutely be C0G, or film. Otherwise, low leakage like UKL's.

-Take extreme care of DEM capacitors return currents.

-Minimise loop length for all current return paths, loop inductance

-Decouple all ICs locally with smaller value ceramic cap that is close to the pin.

-The DGND should be connected only on place with the AGND pin right next to the input pins (pin 4 or 5 or something). Dont just do a whole copper pour and hope for the best, you can get good results this way also but only if your layout is good. Basically you can do two copper pours, one for digital and one for analog, and both should be connected in the area between these two pins on the DAC itself. But you must at the same time take care of DEM cap return currents, this necessitates 4 layers.

That is off the top of my head, there is more if you spend reading thread...but its enough to make a good dac for starters.

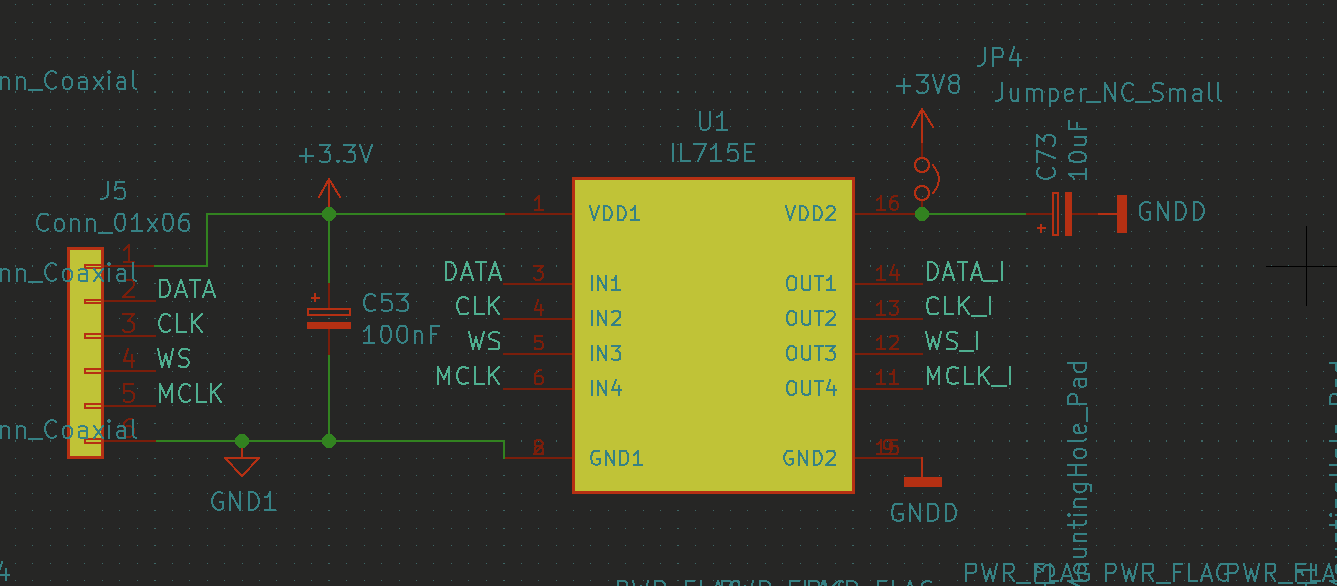

And also as grund said, do this. You can use IL715 easily, i used it when i made starting project like you now.Separate the power supply of the DIR9001 itself from the rest. Try that DIR9001 has its own secondary on the transformer. This is the difference between an ordinary and top-quality DAC, as well as the quality of the regulator.

Thank's Dendrobium , I already disconnect the DIR9001 supply from the logic section , but why using the IL715 in my setup , knowing that I am not running I2S protocol

.

.

I just show my example, you can put SPDIF instead of I2S. IL715 is generic high speed digital isolator. I did not look detailed at what you're doing, so take what you think is applicable from it.

Ok , I think I wont need an digital isolator as this setup has been made by John without and was working as is , my concern is more about the routing itself

.

.

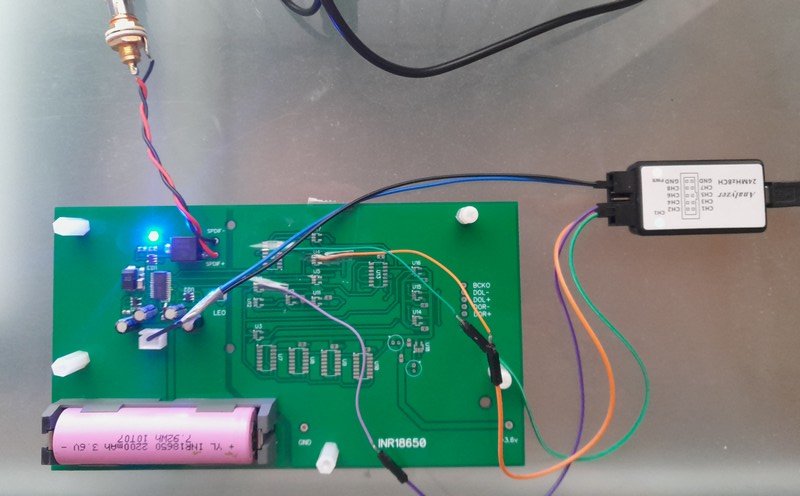

Well , I solve the power supplies separating problem and the 5 v regulators problems , I remenber I had a bunch of INR18650 2 Ah cells 😉

.

.

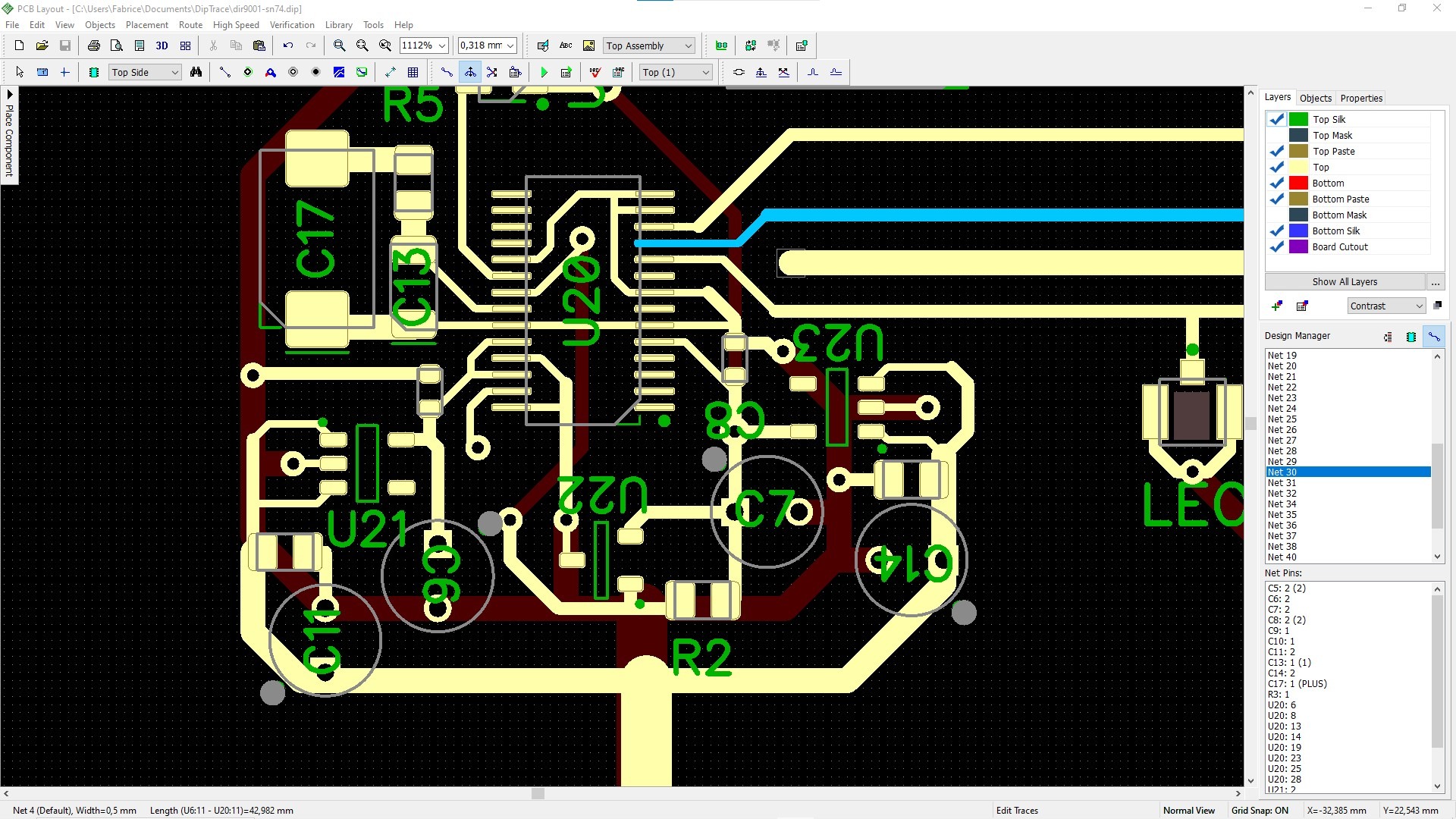

@ Grunf , am I good now with the pll and groundings :

there is so little space to do it right !!

there is so little space to do it right !!

Question about CM6631A - it has two SPDIF inputs and outputs. What is the purpose of the extra receiver? Or it can not get stream from spdif and out it to i2c dac.

38 XSPDIFO_0 DO S/PDIF transmitter Programmable 3.3V output buffer

40 XSPDIFI_0 DI S/PDIF receiver 3.3v input buffer, Schmitt trigger, pull-down

38 XSPDIFO_0 DO S/PDIF transmitter Programmable 3.3V output buffer

40 XSPDIFI_0 DI S/PDIF receiver 3.3v input buffer, Schmitt trigger, pull-down

Hi all ,

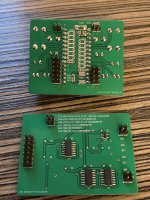

After having controled hundred times my pcb routing , I finally make them build by jlcpcb , they make a good job for the money 😉

I decided to populate the pcb's step by step , so here is the dir9001 section and the result is ok , next I will populate the logic section and see how it goes

the spdif source is the digital output of an cd player

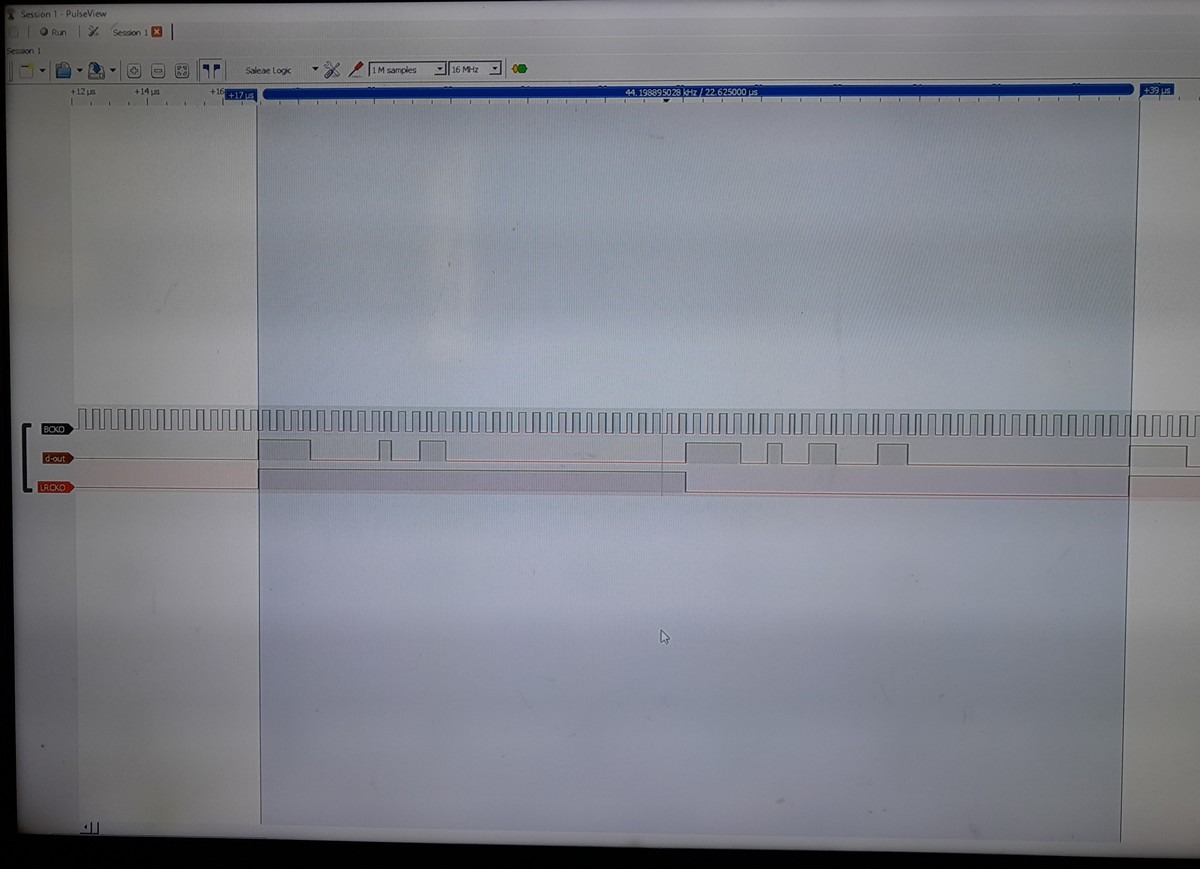

here is part of the logic view :

.

After having controled hundred times my pcb routing , I finally make them build by jlcpcb , they make a good job for the money 😉

I decided to populate the pcb's step by step , so here is the dir9001 section and the result is ok , next I will populate the logic section and see how it goes

the spdif source is the digital output of an cd player

here is part of the logic view :

.

Last edited:

Here is the logic frame , left justified protocol , bcko at 128 fs , and fs at 44.19 Khz

.

.

Last edited:

Hi

that LE line looks normal for the Left justified format. (These LE lines form previous pistures are not OK...)

But maybe before TimeSim adapter You need I2S format?

That is almost the same as left just, with MSB is 1 BCK data delay from LE line

that LE line looks normal for the Left justified format. (These LE lines form previous pistures are not OK...)

But maybe before TimeSim adapter You need I2S format?

That is almost the same as left just, with MSB is 1 BCK data delay from LE line

The previous picture (post 8216 ) was not good , contact issues was occuring and sample rate was off

fact is that this project , as it start at post 6116 is meant to run with left justified , for many reasons explain all along this thread , I2S as much as I understood is noisy , this setup is complex enought to bring in issues like noises and stuff 🙂

.

fact is that this project , as it start at post 6116 is meant to run with left justified , for many reasons explain all along this thread , I2S as much as I understood is noisy , this setup is complex enought to bring in issues like noises and stuff 🙂

.

Last edited:

Hi, building my dac: TDA1541a (50Hz DEM mod) with I2S to simultaneous converter. Each power supply voltage will be final regulated by Jung-Didden super regulators, these will be fed by LM317/337 pre-regulators.

I2S signal is generated by a raspberry Pi 4, a Ian Canada shieldpi pro and Fifopi Q7.

IV converter not sure yet, but tend to go with the discrete diamond of Pedja Rogic discrete.

I2S signal is generated by a raspberry Pi 4, a Ian Canada shieldpi pro and Fifopi Q7.

IV converter not sure yet, but tend to go with the discrete diamond of Pedja Rogic discrete.

Attachments

- Home

- Source & Line

- Digital Line Level

- Building the ultimate NOS DAC using TDA1541A