Hi JMF11, I understand the design in the following way:

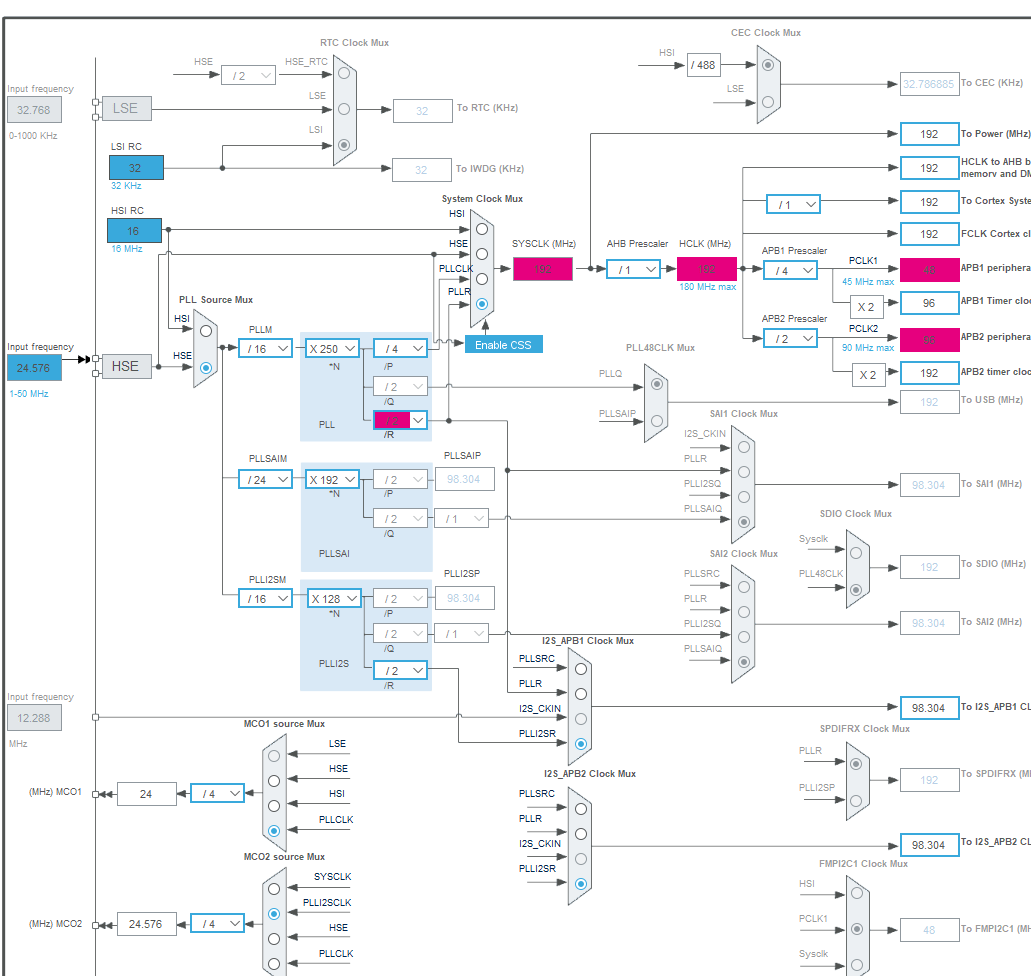

one 48k family xtal (24.572) to generate:

24M for USB

44.1k family

48k family

with a specific configuration of main pll:

Above the conf for 48k family and right clokcing for USB

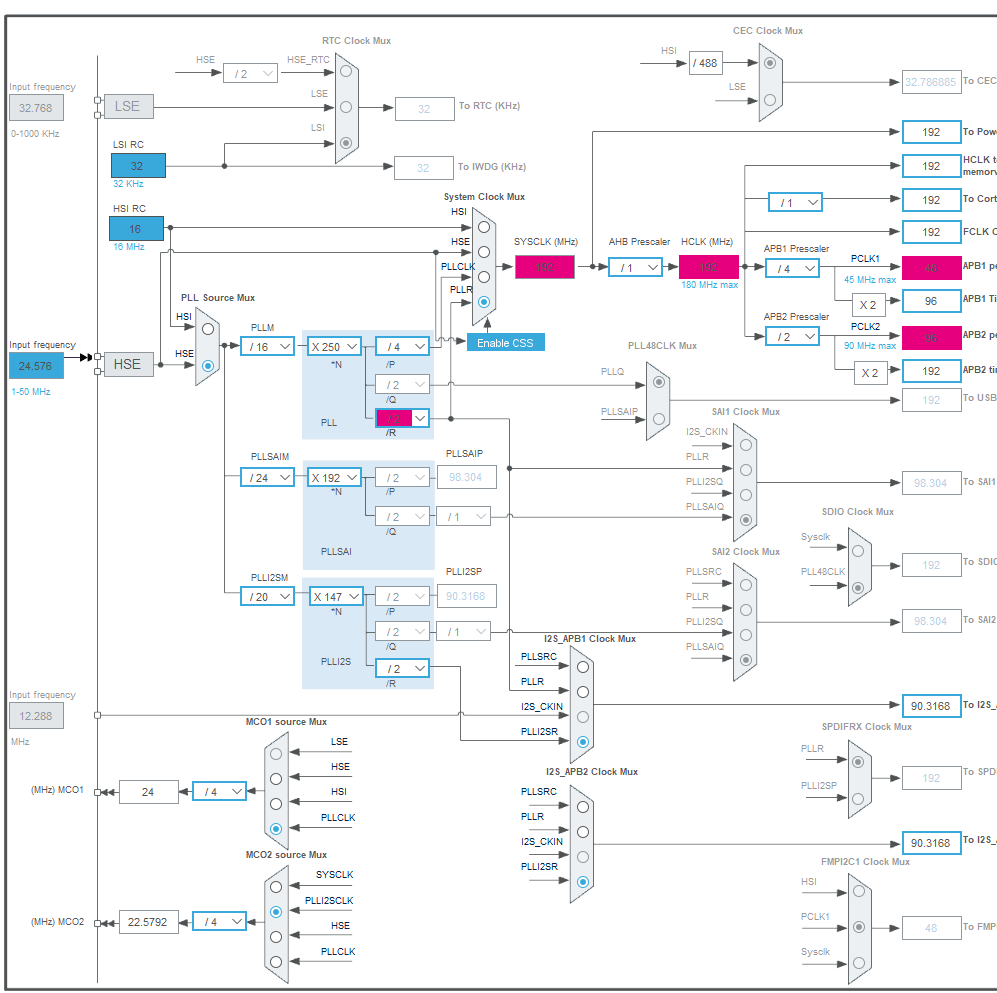

And the conf for 44.1 family

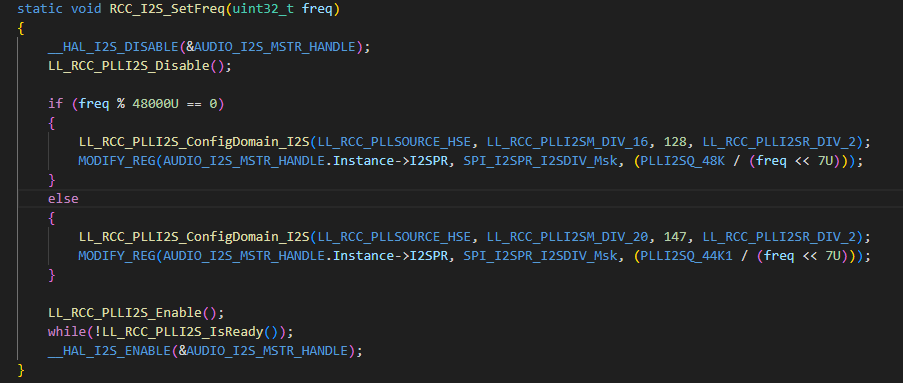

Code change PLLI2SM conf with a function call defined in USB_DEVICE/App//usbd_audio_if.c

The is a little bit of overclocking to achieve that, anyway this should'nt be a big deal for the target.

Two configs in usb descriptor, maybe one for standard PCM/I2S, the other for DoP/DSD?

one 48k family xtal (24.572) to generate:

24M for USB

44.1k family

48k family

with a specific configuration of main pll:

Above the conf for 48k family and right clokcing for USB

And the conf for 44.1 family

Code change PLLI2SM conf with a function call defined in USB_DEVICE/App//usbd_audio_if.c

The is a little bit of overclocking to achieve that, anyway this should'nt be a big deal for the target.

Two configs in usb descriptor, maybe one for standard PCM/I2S, the other for DoP/DSD?