Just order the accusilicons Kartick

You still will have a fantastic DAC, sounding better than almost everything out there ! Don’t get carried away by “ultimate” experiments... Those are very nice to have, but not a must...

No worries, your newly implemented DAC will not sound like a shower radio without the super expensive top of the bill clocks

You still will have a fantastic DAC, sounding better than almost everything out there ! Don’t get carried away by “ultimate” experiments... Those are very nice to have, but not a must...

No worries, your newly implemented DAC will not sound like a shower radio without the super expensive top of the bill clocks

If now all great upgrades will be combined into one new board system, it will be become a super high end and expensive solution for a smaller group of people.

As it is, the DDDAC just takes an I2S signal, and people can experiment with the I2S source to their hearts' content. If this would all be incorporated within the DDDAC main board, this flexibility for tweaking and upgrading stuff would be lost. Not good. Leave the DDDAC concept as it is!

In terms of clocks.... thanks for all the tests you did and expressing where "easy" gain is to be made and how difficult it is to get the last juice squeezed out of better clocks.

All this (also before your post) made me think to get a reasonable solution for maximum clock specs but as a compromise to have simple implementation for most of the DDDAC and fifo users.

That would be super cool! I can take an IAN FiFo and plug in some Accusilicons, okay. I can also do a lot more, if I find sufficiently clear information and the suitable parts -- and this is exactly where I am stuck at the moment. I am looking forward to your work in this direction!

Just order the accusilicons Kartick

You still will have a fantastic DAC, sounding better than almost everything out there ! Don’t get carried away by “ultimate” experiments... Those are very nice to have, but not a must...

No worries, your newly implemented DAC will not sound like a shower radio without the super expensive top of the bill clocks

Super DD!! The order will be punched in right away!!

Yuri, thanks you for your work and sharing your experience. That was very helpful in expectation setting of the use of different clocks

Indeed a good point you make on the clock frequency, whether we should take 22/24 or 45/49 families to play max 192FS or 384FS tracks on the fifopi - but having said so, you do not want to change your clocks again in a few years if this 384FS becomes a thing. But point made and everyone can make his own decision. Like some just take 5Mhz family as the only listen to 44.1 tracks

Your "request" for the Motherboard is of course something I have contemplated many times the past years (no surprise I hope?)

I decided against it, as I want the DDDAC modular concept to be able to give a broad audience access to a great sounding DAC for a very reasonable price.

If now all great upgrades will be combined into one new board system, it will be become a super high end and expensive solution for a smaller group of people.

for this group however, there is the way of relatively easy DIY (hence this forum) - and somehow I believe that as soon as you make it "ultimate" a month later there is the new "Ultimate MKII"

What I could do next year, maybe, is doing a crowd funding kind or thing for an "ultimate" MB (and dac module?) design, so I know if it will be worth the cost and effort - this could even integrate a FiFoPi kind of thing as "all in one" - let's see....

In terms of clocks.... thanks for all the tests you did and expressing where "easy" gain is to be made and how difficult it is to get the last juice squeezed out of better clocks.

All this (also before your post) made me think to get a reasonable solution for maximum clock specs but as a compromise to have simple implementation for most of the DDDAC and fifo users. See / read post of "mbrennwa" why this might be a point.

I will pick this up (for personal reasons) in January. The idea is (was?) to get 45/49 XO DIL14 clocks working in the Q3 fifopi with -115dB @ 10Hz. This should be probably the best you can get for easy DIY and having a very nice leap in SQ (??) Of course to be tested, and again a major time and $ investment from my side, so I am still not 100% on this, but we will see. Your experience shows it might indeed be the case that will give this nice jump in SQ. It need to be worth it ! 22/24 families probably will do a few dB better - but see my point earlier. (In case of a 11MHz family, the XO will do roughly -123dB by the way) This would allow for at least 88 and 96 FS...

But to dampen any euphories, this will come at a cost... end user price for such a XO will probably be between 400 and 500 Euro / single XO clock

as we say "to be cont'd"

You can count on me joining the party if you do this next year Doede

@kartick

You chose absolutely Ok. Well, maybe I have not clarified my message. I think what NDK*SDA (used it a long time!) is 3 times cheaper with the same performance, BUT it comes with a very small package, so I can recommend it only if you have a soldering station.

And one more thing. Many people on this forum wrote about successful upgrades. "Now it sounds much better!". Reality is many times worse: if it really was searching for the best solution, using a lot of variants, it's experimentation, and expensive losses are inevitable Not a good starting point anyway.

Not a good starting point anyway.

@Doede

It's clear, what modular design is better, large community with non-extra-high end starting point generate more ideas than small community with ultra-high starting point. The question is how to achieve modular design that can be used for next-level upgrades . In my opinion, 7805-style regs in DDDAC kit -- brilliant solution. Clean power is essential, but each step for better power, especially in paralleled DACs setup is very expensive too.

. In my opinion, 7805-style regs in DDDAC kit -- brilliant solution. Clean power is essential, but each step for better power, especially in paralleled DACs setup is very expensive too.

My starting point was 44/49 clocks -- that's what I need. As we are in NOS-club, reclocker IC acts as freq. divider too, so with exceptional good implementation at 192k we may expect -6db to noise performance and so on. It will be better if it is possible to achieve the same performance and more compatible with higher speeds (anyway, gain in SQ of it is questionable), but price rises quickly with every -1dB at 10 Hz for 45/49 clocks. As I started comparing clock performance graphs a long time ago, I planned to show it here, just checked it, something changed on the market, so I need to verify it.

And some thoughts about ultra-high-quality XO directly on Fifo.

1. There are differences in implementation of "audio" XO (like Crystek) and "professional" XO. In the first case, XO internal schematic completely turned off when you change OE pin state. Most professional XOs act in another way. Their schematic still works, oscillation still works, OE turns off only the last gate of their output buffer. It's better for the clock stability especially for a long term (anyway, most prof. XO are graded for long-term stability too), but it means leakage of “unused” clock signal into a common clock’s power line. In technical terms the schematic will work, except the noise performance of expensive XO will be degraded. As I know, some high-end-class DAC developers encountered this problem, at least this effect is measurable. So, there are at least two options: 1. separated power rails for each XO. 2. Unused XO must be completely turned off. In my opinion, for Ian's boards additional "proxy PCB" to deal with it is needed. Not a big problem. And proxy pcb means what form-factor of XO is no more limited by FIFO’s sockets

2. I did not plan to comment on this topic, even if it can be helpful. Too many fights between Ian and Andrea in other threads. Well... I confirm Andrea's measurements. For this extremely HQ clock, with low noise digital regs in DDDAC and many other upgrades, bottle-neck in my setup was reclocking of BCK in FIFO.

(remark to @all_readers)

To prevent any possible future discussion on this topic: Level, where it can be noticeable: Pulsar clock, Andrea's clock, Rutger's clock, extremely expensive clocks ($500+). I appreciate Ian's works, and I appreciate Andreas' works too. I use Ian's and Andrea's solutions, I like it, I’ll use it in the future. It's my non-standard setup, I use McFIFO where option of a custom reclocker is declared in manual, it's not an all-in-one solution as FifoPi. if some guys with new Andrea's clocks or any other ultra-HQ clock with non-standard setup encountered with this, for DDDAC users easy and inexpensive fixes described several posts above in this thread. At least at -127db@10Hz for 22/24MHz clock it works fine. Sorry, no way to achieve top-level clock performance simply buying DDDAC kit, FIFO and Andrea's kits in the current situation. Nothing wrong with FIFO, DDDAC, clock. No future comments from me on this topic, sorry.

@Doede

Returning to the topic, for super-next-level DDDAC in my opinion FIFO is great, but it’s better to consider the option “clocks outside FIFO socket”

You chose absolutely Ok. Well, maybe I have not clarified my message. I think what NDK*SDA (used it a long time!) is 3 times cheaper with the same performance, BUT it comes with a very small package, so I can recommend it only if you have a soldering station.

And one more thing. Many people on this forum wrote about successful upgrades. "Now it sounds much better!". Reality is many times worse: if it really was searching for the best solution, using a lot of variants, it's experimentation, and expensive losses are inevitable

@Doede

It's clear, what modular design is better, large community with non-extra-high end starting point generate more ideas than small community with ultra-high starting point. The question is how to achieve modular design that can be used for next-level upgrades

My starting point was 44/49 clocks -- that's what I need. As we are in NOS-club, reclocker IC acts as freq. divider too, so with exceptional good implementation at 192k we may expect -6db to noise performance and so on. It will be better if it is possible to achieve the same performance and more compatible with higher speeds (anyway, gain in SQ of it is questionable), but price rises quickly with every -1dB at 10 Hz for 45/49 clocks. As I started comparing clock performance graphs a long time ago, I planned to show it here, just checked it, something changed on the market, so I need to verify it.

And some thoughts about ultra-high-quality XO directly on Fifo.

1. There are differences in implementation of "audio" XO (like Crystek) and "professional" XO. In the first case, XO internal schematic completely turned off when you change OE pin state. Most professional XOs act in another way. Their schematic still works, oscillation still works, OE turns off only the last gate of their output buffer. It's better for the clock stability especially for a long term (anyway, most prof. XO are graded for long-term stability too), but it means leakage of “unused” clock signal into a common clock’s power line. In technical terms the schematic will work, except the noise performance of expensive XO will be degraded. As I know, some high-end-class DAC developers encountered this problem, at least this effect is measurable. So, there are at least two options: 1. separated power rails for each XO. 2. Unused XO must be completely turned off. In my opinion, for Ian's boards additional "proxy PCB" to deal with it is needed. Not a big problem. And proxy pcb means what form-factor of XO is no more limited by FIFO’s sockets

2. I did not plan to comment on this topic, even if it can be helpful. Too many fights between Ian and Andrea in other threads. Well... I confirm Andrea's measurements. For this extremely HQ clock, with low noise digital regs in DDDAC and many other upgrades, bottle-neck in my setup was reclocking of BCK in FIFO.

(remark to @all_readers)

To prevent any possible future discussion on this topic: Level, where it can be noticeable: Pulsar clock, Andrea's clock, Rutger's clock, extremely expensive clocks ($500+). I appreciate Ian's works, and I appreciate Andreas' works too. I use Ian's and Andrea's solutions, I like it, I’ll use it in the future. It's my non-standard setup, I use McFIFO where option of a custom reclocker is declared in manual, it's not an all-in-one solution as FifoPi. if some guys with new Andrea's clocks or any other ultra-HQ clock with non-standard setup encountered with this, for DDDAC users easy and inexpensive fixes described several posts above in this thread. At least at -127db@10Hz for 22/24MHz clock it works fine. Sorry, no way to achieve top-level clock performance simply buying DDDAC kit, FIFO and Andrea's kits in the current situation. Nothing wrong with FIFO, DDDAC, clock. No future comments from me on this topic, sorry.

@Doede

Returning to the topic, for super-next-level DDDAC in my opinion FIFO is great, but it’s better to consider the option “clocks outside FIFO socket”

teaser

talking about upgrades, first promising tests with my new prototype mainboard are through

For the interested:

I will make a complete "report" once everything is in place and I finished building the demagnetizer for my sowters ;>

Greetings oli

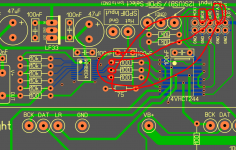

talking about upgrades, first promising tests with my new prototype mainboard are through

For the interested:

- Right justified directly from the raspberry pi

- Option to input without or with buffer (74AC244), seems to work fine without buffer with 4 boards

- "LR inverted" instead of "delayed Data" for left/right seperation

- Matched the length of the signal lines as close as possible. Idea was that the eliminating of random jitter trough parallel chip design works the best if these line lengths match. Otherwise it can happen that the following chip fires every time after the "jitter window" of his predecessor and could then have no influence on the random jitter (hope this is understandable and makes sense ;D)

I will make a complete "report" once everything is in place and I finished building the demagnetizer for my sowters ;>

Greetings oli

Attachments

Matched the length of the signal lines as close as possible. Idea was that the eliminating of random jitter trough parallel chip design works the best if these line lengths match. Otherwise it can happen that the following chip fires every time after the "jitter window" of his predecessor and could then have no influence on the random jitter (hope this is understandable and makes sense ;D)

Uhm, I don't get it. Why would different lengths matter? How does this affect random phase noise (jitter)?

First off all I'm not sure if this has an effect on random jitter, perhaps we can find out here The equal length was mainly for helping with signal integrity. Which is kind of important the way the signals are distributed here: without fan out or buffer chips.

The equal length was mainly for helping with signal integrity. Which is kind of important the way the signals are distributed here: without fan out or buffer chips.

Now to the idea:

If you have a look at Doedes homepage under "other" you can see a nice explanation for the idea behind paralleling DAC-Chips.

So in theory, if you want a new sequence of DAC-chips in every sample, you don't want to deliver the signal with a delay to some of them.

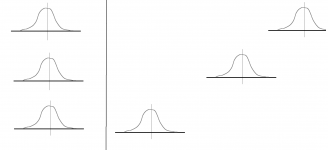

For better understanding and showing of my paint skills i attached a little sketch; where left is signal at every chip at the same time and the right side symbolizes unequal length/delay between chips ;D

Now to the idea:

If you have a look at Doedes homepage under "other" you can see a nice explanation for the idea behind paralleling DAC-Chips.

So in theory, if you want a new sequence of DAC-chips in every sample, you don't want to deliver the signal with a delay to some of them.

For better understanding and showing of my paint skills i attached a little sketch; where left is signal at every chip at the same time and the right side symbolizes unequal length/delay between chips ;D

Attachments

depends on multiple things but it shouldl be around 15cm/ns, so if jitter is in the low ps region there is not much tolerance for line length differences

edit: the black magic bible says in PCB the delay is 140-180ps/in (picosecondes delay per inch trace length)

edit: the black magic bible says in PCB the delay is 140-180ps/in (picosecondes delay per inch trace length)

Last edited:

While my order from Audio Creative is on the way (PSU + mainboard + DACx2)

Can't stop ... I got some extra components for the Mauser. Audio hobby will finish me off.

It remains to decide on I / V resistors, Audio Note or Rhopoints.

Well, the transformer may be in the next year, Sowter by Doede or 9335 not decided yet.

Can't stop ... I got some extra components for the Mauser. Audio hobby will finish me off.

It remains to decide on I / V resistors, Audio Note or Rhopoints.

Well, the transformer may be in the next year, Sowter by Doede or 9335 not decided yet.

While I await my order comprising of the Fifopi and clocks to reach me from Audiophonics.fr, I was just thinking that since the fifopi will be interfacing between the WaveIO and DDDAC's motherboard, it should not be helping in any way on the SPDIF input signal. Because my cdp gives spidf out to Dac's spidf IN and that goes directly to the motherboard. So net net the ian's fifopi only reclocks the usb signal and not the coax signal.

Is that understanding correct?

Is that understanding correct?

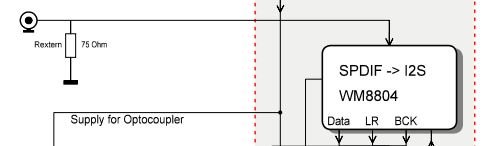

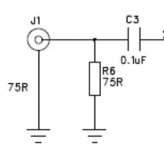

yes this correct Kartick, UNLESS you would pick up the I2S at the output of the spdif WM8804 chip on the motherboard and lead them to the input of the FiFoPi..

in that case you could even do a A-B comparison by switching back and forward

in that case you could even do a A-B comparison by switching back and forward

Attachments

- Home

- Source & Line

- Digital Line Level

- A NOS 192/24 DAC with the PCM1794 (and WaveIO USB input)