Hi everybody,

this is my first post ever.

I would like to add a minor but my be interesting remark to shielding subject.

As I remember correctly, a very effective way of shielding is to apply a two layers of materials,

while looking from source of radiation side use first diamagnetic/paramagnetic than ferromagnetic material,

like copper/aluminum and steel screen. So if we would like protect our circuit against external electromagnetic field

it is good to use aluminum or copper screen first and inside secondary steel enclosure.

this is my first post ever.

I would like to add a minor but my be interesting remark to shielding subject.

As I remember correctly, a very effective way of shielding is to apply a two layers of materials,

while looking from source of radiation side use first diamagnetic/paramagnetic than ferromagnetic material,

like copper/aluminum and steel screen. So if we would like protect our circuit against external electromagnetic field

it is good to use aluminum or copper screen first and inside secondary steel enclosure.

Hi takek,...if we would like protect our circuit against external electromagnetic field...

A couple of comments:

1. In some cases at least part of the EM noise source is inside the dac case rather than external.

2. The kind of shielding you mention used to be used to shield magnetic tape heads. In that case there were often more than 2-layers of different metals. However, that type of shield tends to be costly and may be more than is really needed for a dac.

Thank you for posting about it though

Also, can I ask where you learned about that type of layered shielding? Just curious if there is a good reference on the subject.

Simple

https://www.edn.com/multi-layer-shields-improve-shielding-effectiveness/

https://www.osti.gov/servlets/purl/1592859

Advanced

https://escholarship.org/content/qt1h04v335/qt1h04v335_noSplash_f5eaee31bbc3802a0791ade8dd29dcff.pdf

https://cds.cern.ch/record/826957/files/phess-2005-006.pdf

https://www.mdpi.com/2079-9292/11/24/4156/pdf

George

https://www.edn.com/multi-layer-shields-improve-shielding-effectiveness/

https://www.osti.gov/servlets/purl/1592859

Advanced

https://escholarship.org/content/qt1h04v335/qt1h04v335_noSplash_f5eaee31bbc3802a0791ade8dd29dcff.pdf

https://cds.cern.ch/record/826957/files/phess-2005-006.pdf

https://www.mdpi.com/2079-9292/11/24/4156/pdf

George

Last edited:

@Markw4

Over 30 years ago while living in Poland I had a book ( translated from Russian language )

from which I memorized that. Unfortunately during relocation to US I have lost it, and don't remember

author or title.

@gpapag

Thank You for posting these links. I have saved documents and already started read them.

Initially I hesitate to post something what is not really precise, but it turns to be beneficial for myself,

because now I am inspired to learn more...

BTW This is a great thread, packed with a lot of information and knowledge.

I

Over 30 years ago while living in Poland I had a book ( translated from Russian language )

from which I memorized that. Unfortunately during relocation to US I have lost it, and don't remember

author or title.

@gpapag

Thank You for posting these links. I have saved documents and already started read them.

Initially I hesitate to post something what is not really precise, but it turns to be beneficial for myself,

because now I am inspired to learn more...

BTW This is a great thread, packed with a lot of information and knowledge.

I

I don't know when I will have the time to actually do it, but here is what I will do:

I'll take my old preamplifier from the attic. It is completely discrete, single-ended and class A and has a headphone amplifier built in.

View attachment 1202822

I'll hook it up single-endedly (it only has single-ended inputs anyway) to the prototype RTZ shift register FIRDAC, which I will modify such that I can use my ABX switchbox to switch between large and small common-mode loop bandwidth. The FIRDAC will be driven from the digital part of my earlier solid-state DAC, which will be driven from the S/PDIF output of a DVD player. Everything is double insulated, so there will be no ground loops.

I'll do 20 trials with the digital part of the solid-state DAC in PWM8 mode (which results in a relatively clean out-of-band spectrum; lots of noise but no idle tones or other aberrations) and 20 with it in chaotic mode and report the raw results.

Today I hooked up the DAC to the digital part of the earlier solid-state DAC and to my old preamplifier (with no ABX box yet). A problem I overlooked is that as soon as I connect a big electrolytic capacitor in parallel with the 15 pF of the common-mode loop to slow down the loop, there is a tick because the electrolytic capacitor needs to settle to the right voltage. When you disconnect it and connect it again, there is a much softer but still audible tick, presumably because leakage and dielectric absorption make the voltage across the electrolytic capacitor change slowly when it is not connected.

Edit: I can probably reduce the voltage jump to a fraction of the OPA210's offset voltage by keeping one side of the big capacitor permanently connected to the OPA210 output and switching the other side between virtual ground and a resistor to (non-virtual) ground. To be continued.

Last edited:

Marcel, just to be clear did you change the resistors too, to 1M?

So thread readers may more easily understand what we are talking about, pics at: https://www.diyaudio.com/community/...t-register-firdac.379406/page-65#post-7426445

So thread readers may more easily understand what we are talking about, pics at: https://www.diyaudio.com/community/...t-register-firdac.379406/page-65#post-7426445

Hi all,

... Following up on my post #1888 on how I made the external clock connection to the JLSounds' board. However, as it is I cannot find the actual files for the design on my computer (I vaguely remember it being "corrupted" when upgrading from Kicad 5 to Kicad 6) so I will instead give a description of the circuitry.

First, the inverter: I here used the U74AC04 fed from one of Andrea Mori's 22/24 MHz oscillators. The U74AC04 sent out one signal line to an NC7WZ16 where I used one channel to feed a CY2302 clock multiplier (the JLSounds' board needs an input frequency of 45/49 MHz). This clock multiplier was implemented in a way so that I could shift the multiplication factor from 2x to 8x - thus presumably (see below) allowing me to use any of Andrea's oscillators from 5/6 MHz to 22/24 MHz.

As the JLSounds' ExMclk input has a relatively low ohmic resistance (~510 ohms, resistor) I included a buffer between the CY2302 and the JLSounds' board (another NC7WZ16, single channel). Incidentally, with the correct settings of the JLSounds' setting pins, I have found that this ExMclk input works flawlessly (3.3 V input levels required).

Going out of the JLSounds' board I left the data & LRCK lines unaltered but for the BCLK I included another U74AC04 connected so that I could both invert and variably delay this BCLK signal. In this way I could time-align the BCLK coming from the JLSounds' board and the "MCLK" coming from the first U74AC04 (with Andrea's oscillator).

Thus with a time-aligned BCLK now coming from the JLSounds' board and a MCLK coming from the U74AC04 inverter I then used an NC7SZ374 single FF to perform the re-clocking function. And then from this FF to a group of output pins that also included the JLSounds' board data and LRCK lines (not an optimum connection I think, but for a trial OK).

I used 4VDC for all circuitry except for the signal line going into the ExMclk pin - checking the CPLD datasheet I think using 4 volts here might damage the CPLD. However, a more feasible PSU voltage range probably would be 5V for the inverter U74AC04, 4V for the NC7WZ16 (connecting to) and the CY2302, 3.3V for the NC7WZ16 going into the ExMclk pin, and 4-5 VDC for the time-alignment U74AC04 and the NC7SZ374 reclocking IC.

The caveat: This all works quite well, however, with one important caveat! ... Upsampling the incoming oscillator frequency means that for every doubling of the oscillator frequency the "PLL" inside the JLSounds' board may choose either of the available rising edges. Thus, if the incoming oscillator is e.g. 24.5 MHz when doubled there will be two rising edges that the JLSounds' "PLL" may lock on to. If the incoming oscillator frequency is 6.1 MHz (8x multiplication) there will be eight edges to lock on to ...

And, since the JLSounds' board at least to some extent synchronizes the other data lines (DSDR, DSDL, DSDCLK, and to some extent PCM, according to the I2S protocol) with the locked-on-to rising edge this may cause some misalignment between data and clock lines. Which, at higher sampling frequencies may also cause the NC7SZ374 to consistently reclock the "LOW" level BCLK signals coming from the JLSounds' board. The result of this essentially being no clock on the output of the NC7SZ374

I have had a bit of exchange about this with Andrea Mori and as far as I understand his understanding is that for a 24 MHz clock being reclocked the maximum reliable sampling frequency will be PCM192k or DSD256 (PCM384k with the JLSounds' board configured for PCM1704, etc., mono outputs, my comment).

Also, again to my memory, I found that the DSDCLK signal from the JLSounds' board could change phase between playback instances thus making it at least a bit more challenging to implement some kind of "edge comparison & time-alignment" circuitry that would re-align the inverter edges with the JLSounds' DSDCLK edges.

In practice I found DSD128 to always work reliably, and to my memory also DSD256 (computer speed limited with the more challenging HQPlayer modulators) whereas DSD512 was quite haphazard.

For those who may be interested in trying out this - and would just like a straight forward solution - I hope it is OK with JLSounds that I say that there is a JLSounds' firmware update to the board which allows it to work directly with an incoming 22/24 MHz signal (you may of course already know about this). Thus no multipliers, odd edge alignment, etc. Maximum output rates will then be PCM384k and DSD256.

So, I hope I got all of the above right ... however, this is the way I implemented a reclocking circuitry.

Cheers, Jesper

... Following up on my post #1888 on how I made the external clock connection to the JLSounds' board. However, as it is I cannot find the actual files for the design on my computer (I vaguely remember it being "corrupted" when upgrading from Kicad 5 to Kicad 6) so I will instead give a description of the circuitry.

First, the inverter: I here used the U74AC04 fed from one of Andrea Mori's 22/24 MHz oscillators. The U74AC04 sent out one signal line to an NC7WZ16 where I used one channel to feed a CY2302 clock multiplier (the JLSounds' board needs an input frequency of 45/49 MHz). This clock multiplier was implemented in a way so that I could shift the multiplication factor from 2x to 8x - thus presumably (see below) allowing me to use any of Andrea's oscillators from 5/6 MHz to 22/24 MHz.

As the JLSounds' ExMclk input has a relatively low ohmic resistance (~510 ohms, resistor) I included a buffer between the CY2302 and the JLSounds' board (another NC7WZ16, single channel). Incidentally, with the correct settings of the JLSounds' setting pins, I have found that this ExMclk input works flawlessly (3.3 V input levels required).

Going out of the JLSounds' board I left the data & LRCK lines unaltered but for the BCLK I included another U74AC04 connected so that I could both invert and variably delay this BCLK signal. In this way I could time-align the BCLK coming from the JLSounds' board and the "MCLK" coming from the first U74AC04 (with Andrea's oscillator).

Thus with a time-aligned BCLK now coming from the JLSounds' board and a MCLK coming from the U74AC04 inverter I then used an NC7SZ374 single FF to perform the re-clocking function. And then from this FF to a group of output pins that also included the JLSounds' board data and LRCK lines (not an optimum connection I think, but for a trial OK).

I used 4VDC for all circuitry except for the signal line going into the ExMclk pin - checking the CPLD datasheet I think using 4 volts here might damage the CPLD. However, a more feasible PSU voltage range probably would be 5V for the inverter U74AC04, 4V for the NC7WZ16 (connecting to) and the CY2302, 3.3V for the NC7WZ16 going into the ExMclk pin, and 4-5 VDC for the time-alignment U74AC04 and the NC7SZ374 reclocking IC.

The caveat: This all works quite well, however, with one important caveat! ... Upsampling the incoming oscillator frequency means that for every doubling of the oscillator frequency the "PLL" inside the JLSounds' board may choose either of the available rising edges. Thus, if the incoming oscillator is e.g. 24.5 MHz when doubled there will be two rising edges that the JLSounds' "PLL" may lock on to. If the incoming oscillator frequency is 6.1 MHz (8x multiplication) there will be eight edges to lock on to ...

And, since the JLSounds' board at least to some extent synchronizes the other data lines (DSDR, DSDL, DSDCLK, and to some extent PCM, according to the I2S protocol) with the locked-on-to rising edge this may cause some misalignment between data and clock lines. Which, at higher sampling frequencies may also cause the NC7SZ374 to consistently reclock the "LOW" level BCLK signals coming from the JLSounds' board. The result of this essentially being no clock on the output of the NC7SZ374

I have had a bit of exchange about this with Andrea Mori and as far as I understand his understanding is that for a 24 MHz clock being reclocked the maximum reliable sampling frequency will be PCM192k or DSD256 (PCM384k with the JLSounds' board configured for PCM1704, etc., mono outputs, my comment).

Also, again to my memory, I found that the DSDCLK signal from the JLSounds' board could change phase between playback instances thus making it at least a bit more challenging to implement some kind of "edge comparison & time-alignment" circuitry that would re-align the inverter edges with the JLSounds' DSDCLK edges.

In practice I found DSD128 to always work reliably, and to my memory also DSD256 (computer speed limited with the more challenging HQPlayer modulators) whereas DSD512 was quite haphazard.

For those who may be interested in trying out this - and would just like a straight forward solution - I hope it is OK with JLSounds that I say that there is a JLSounds' firmware update to the board which allows it to work directly with an incoming 22/24 MHz signal (you may of course already know about this). Thus no multipliers, odd edge alignment, etc. Maximum output rates will then be PCM384k and DSD256.

So, I hope I got all of the above right ... however, this is the way I implemented a reclocking circuitry.

Cheers, Jesper

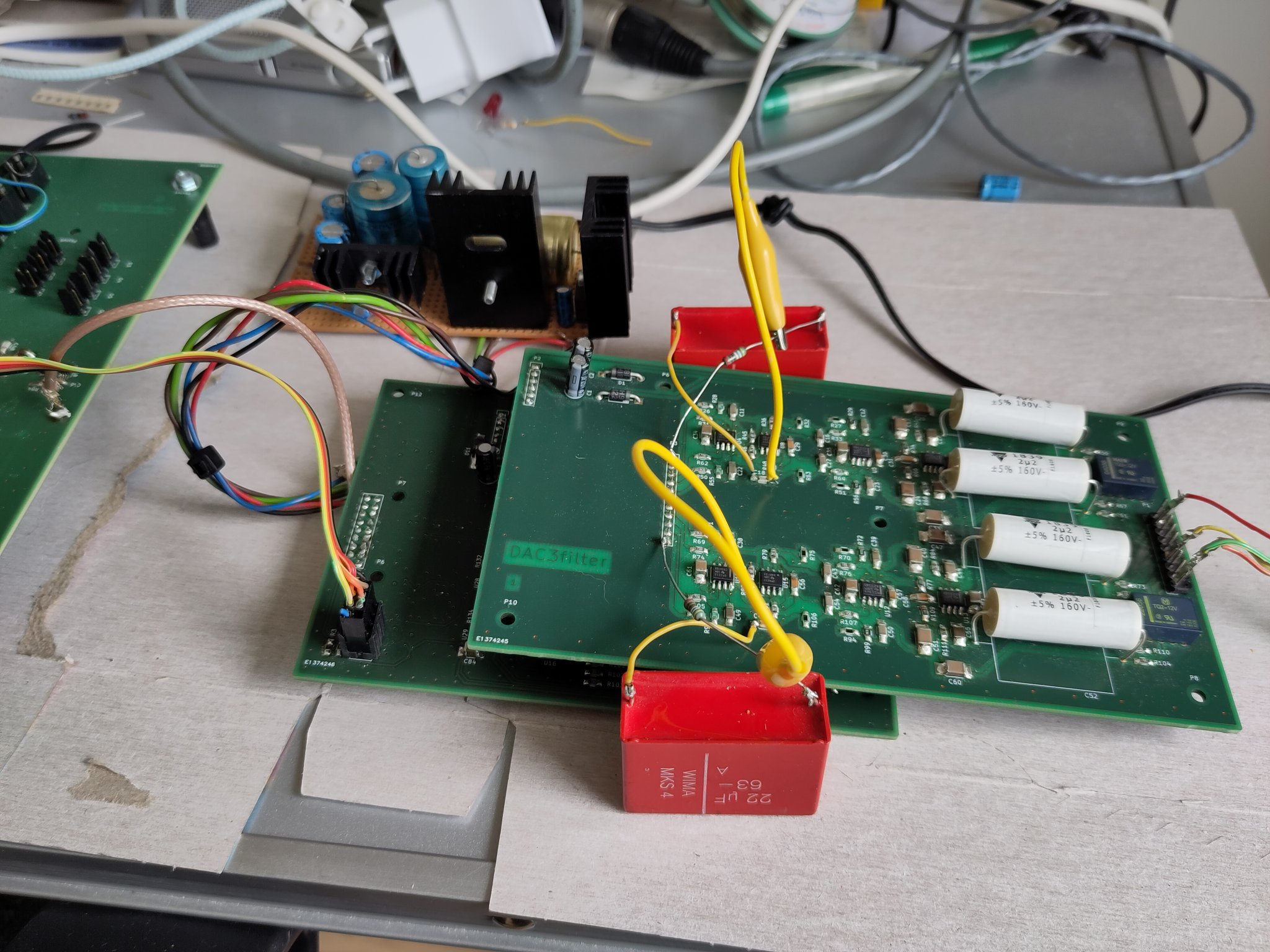

I've replaced the electrolytic capacitors to slow down the common-mode loops with 22 uF, 63 V WIMA MKS 4 film capacitors, added 4.99 kohm metal film resistors to ground to keep the capacitors properly biased and added wires with alligator clips for easy connection and disconnection. It's still a sighted test.

My subjective impression so far is that I hear no difference whatsoever whether the big capacitors are or are not connected - which doesn't mean much, as I'm a middle aged man with tinnitus and I expected not to hear any difference.

My subjective impression so far is that I hear no difference whatsoever whether the big capacitors are or are not connected - which doesn't mean much, as I'm a middle aged man with tinnitus and I expected not to hear any difference.

Hi Marcel,

Thank you for trying.

However, perhaps worth noting I think my experiment and yours may be significantly different. Again what I did is shown in the pic at: https://www.diyaudio.com/community/...t-register-firdac.379406/page-65#post-7426445 The idea was to slow down the common mode attenuation to approximately RC = 1 (which is a pretty good time constant for a DC servo). What I actually ended up with, given parts on hand, was RC = .5, which is calculated from the two 1M resistors in parallel, times the 1uf Wima cap in the pic.

With 22uf and 2k resistors, that would give a time constant of .022, which I think would put the DC servo corner frequency too high up into the audio band such that LF audio, where the ear is sensitive to phase as it affects LF transients, will be incorrectly reproduced. In that sense, even a time constant of .5 that I used is already a bit of compromise.

May I ask if your filter board still had the last stage intact? If so, that may have further made our experiments significantly different in terms of the final sound produced.

Looking at the situation from a different perspective, if we suppose that some people might not be able to tell any difference if the common mode attenuation works up into the MHz region, as verses if it is limited to a DC servo, then why not just make it a DC servo in the first place and leave it at that? Some people will probably hear a beneficial difference in SE mode, and other people might hear no difference. At least some people might benefit.

Mark

Thank you for trying.

However, perhaps worth noting I think my experiment and yours may be significantly different. Again what I did is shown in the pic at: https://www.diyaudio.com/community/...t-register-firdac.379406/page-65#post-7426445 The idea was to slow down the common mode attenuation to approximately RC = 1 (which is a pretty good time constant for a DC servo). What I actually ended up with, given parts on hand, was RC = .5, which is calculated from the two 1M resistors in parallel, times the 1uf Wima cap in the pic.

With 22uf and 2k resistors, that would give a time constant of .022, which I think would put the DC servo corner frequency too high up into the audio band such that LF audio, where the ear is sensitive to phase as it affects LF transients, will be incorrectly reproduced. In that sense, even a time constant of .5 that I used is already a bit of compromise.

May I ask if your filter board still had the last stage intact? If so, that may have further made our experiments significantly different in terms of the final sound produced.

Looking at the situation from a different perspective, if we suppose that some people might not be able to tell any difference if the common mode attenuation works up into the MHz region, as verses if it is limited to a DC servo, then why not just make it a DC servo in the first place and leave it at that? Some people will probably hear a beneficial difference in SE mode, and other people might hear no difference. At least some people might benefit.

Mark

Last edited:

Because from a technical point of view, it's an illogical way to dimension the common mode loop. Of course anyone can build it the way they like, but I'm not going to change it.

Regarding the loop bandwidth, there is more in the loop than just the integrator. The attenuator (3.9 kohm and 680 ohm) and the gain of the first filter stage (at low frequencies 1 + 845 ohm/(3020 ohm/8) if the shift register output resistance is 10 ohm) also play a role. In my case, the loop bandwidth should be about 3.478 Hz (time constant 45.7559 ms).

The last filter stage is intact on my board.

Regarding the loop bandwidth, there is more in the loop than just the integrator. The attenuator (3.9 kohm and 680 ohm) and the gain of the first filter stage (at low frequencies 1 + 845 ohm/(3020 ohm/8) if the shift register output resistance is 10 ohm) also play a role. In my case, the loop bandwidth should be about 3.478 Hz (time constant 45.7559 ms).

The last filter stage is intact on my board.

Last edited:

How about from the perspective of 'human factors engineering?' Could it be logical that way?...from a technical point of view, it's an illogical way to dimension the common mode loop.

https://industri.fatek.unpatti.ac.i...pproach-Stephen-J.-Guastello-Edisi-2-2013.pdf

Last edited:

As promised, I've also done a blind test with my switchbox. Much to my surprise, I had six out of the first eight correct:

A means without 22 uF, B with 22 uF.

First run of tests, Nisi Dominus, PWM8 modulator:

My answer Correct answer

B B

B A

B B

A A

A A

B B

A B

A A

Listening with the music switched off, I found that there was an audible hum in A that wasn't there in B. Rearranging some transformer output wires solved that. Continuing after this change:

After hum fix, Nisi Dominus, PWM8 modulator:

My answer Correct answer

A A

A B

A B

B B

A A

B A

A A

B A

B A

A B

After hum fix, Nisi Dominus, chaotic modulator:

My answer Correct answer

A B

B B

A B

A A

B A

A B

A A

B A

B B

B A

After hum fix, DIY recording of the Rumours mixed chorus, chaotic modulator:

My answer Correct answer

A B

B B

A A

A B

A A

B B

A A

A B

B A

A A

After hum fix, DIY recording of the Rumours mixed chorus, PWM8 modulator:

My answer Correct answer

A B

A B

A A

A A

B A

B A

A B

B A

B A

A A

My main conclusion from the test is that my old preamplifier with built-in headphone amplifier actually sounds pretty good.

A means without 22 uF, B with 22 uF.

First run of tests, Nisi Dominus, PWM8 modulator:

My answer Correct answer

B B

B A

B B

A A

A A

B B

A B

A A

Listening with the music switched off, I found that there was an audible hum in A that wasn't there in B. Rearranging some transformer output wires solved that. Continuing after this change:

After hum fix, Nisi Dominus, PWM8 modulator:

My answer Correct answer

A A

A B

A B

B B

A A

B A

A A

B A

B A

A B

After hum fix, Nisi Dominus, chaotic modulator:

My answer Correct answer

A B

B B

A B

A A

B A

A B

A A

B A

B B

B A

After hum fix, DIY recording of the Rumours mixed chorus, chaotic modulator:

My answer Correct answer

A B

B B

A A

A B

A A

B B

A A

A B

B A

A A

After hum fix, DIY recording of the Rumours mixed chorus, PWM8 modulator:

My answer Correct answer

A B

A B

A A

A A

B A

B A

A B

B A

B A

A A

My main conclusion from the test is that my old preamplifier with built-in headphone amplifier actually sounds pretty good.

Could be a solution to that problem would be put a FIFO buffer between I2SoverUSB I2S outputs and the reclocker inputs. Clock into the FIFO with I2SoverUSB, clock out with Andrea Mori clock. Something like that. Some related info attached below.The caveat: This all works quite well, however, with one important caveat! ... Upsampling the incoming oscillator frequency means that for every doubling of the oscillator frequency the "PLL" inside the JLSounds' board may choose either of the available rising edges. Thus, if the incoming oscillator is e.g. 24.5 MHz when doubled there will be two rising edges that the JLSounds' "PLL" may lock on to. If the incoming oscillator frequency is 6.1 MHz (8x multiplication) there will be eight edges to lock on to ...

Also, some related info at: https://electronics.stackexchange.com/questions/97280/trying-to-understand-fifo-in-hardware-context

Attachments

Jesper, thank You for the very interesting and informative analysis!For those who may be interested in trying out this - and would just like a straight forward solution - I hope it is OK with JLSounds that I say that there is a JLSounds' firmware update to the board which allows it to work directly with an incoming 22/24 MHz signal.

So one question emerges in me: did You try Amanero, which by default can work with the 22/24MHz clocks.. Only DSD256, yes.

For the record, a couple of years ago I did the same thing Jesper described. It was mostly used with my custom AK4499EQ dac. My clocks were always 22/24MHz as it turned out in practice, but the clock multiplier chip could be configured for a range of ratios. Since I was using JL Sounds with normal firmware, I always sent it 45/49Mhz multiplier output. Multiplier was ICS601-01. Knew there might be a potential problem with timing through the reclocker but never had a problem in practice given the way I was using it. Figured I would deal with it later if it ever became an issue for what I was doing. Reason I did not describe it or share a schematic was because of the nature of my NDA agreements. Since Jesper has described how to do it, the scheme is now public knowledge.

In addition, the board I made included two AK4137 ASRCs that could fully software configured. Because I found they had some sensitivity to incoming jitter, I reclocked before each one. Also found they had some sensitivity to power supply noise, but that's another story. The FPGA-based PCM to DSD converter project has made what I did with AK4137 obsolete so I can talk about it now.

In addition, the board I made included two AK4137 ASRCs that could fully software configured. Because I found they had some sensitivity to incoming jitter, I reclocked before each one. Also found they had some sensitivity to power supply noise, but that's another story. The FPGA-based PCM to DSD converter project has made what I did with AK4137 obsolete so I can talk about it now.

Last edited:

- Home

- Source & Line

- Digital Line Level

- Return-to-zero shift register FIRDAC