I guess the point is, there is a question as to where some line should or might be drawn regarding complexity of offered projects.

I think that should be up to people themselves.

But I still think that a project that makes a PCB that is easy to build up by real "Amateurs" on the kitchen table, buying in the hard to DIY modules is more useful to more people.

Thor

Been there done that. Three projects/group buys even. Many hundreds of satisfied builders of devices that actually could be built. It’s your turn!

Last edited:

Maybe I should do something with this.

So that's where they went...

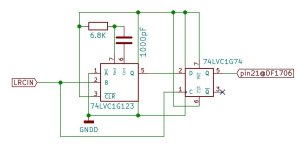

Meanwhile back to the HW IIS to SIM with continuous BCK.

After looking at supplies, I decided to reconsider the FIFO IC, to a single 74ACT2226.

Just like the 74HC40105 TI lists it as active, there is no real stock at TI but plenty (for our use) in the channel.

The 2226 has Half Full Flag indication and 64 bit length.

So we can load two 16 Bit words before clocking out data. plenty of slack.

Flow control probably using a 74HC4040 which can count to 16k (max) and a bit of logic. Need to see.

The word clock basically gates L/R input write enable and also reset's the 4040 for each IIS word.

The first 16 bits after the LRCK Edge are loaded into the FIFO the next 16 bit are gated to input write disable, sending the right bits into the FIFO buffer.

Making a MSB/LE Pulse 4 X IIS BCK wide is also not much logic from the 4040. Also, we have HF Flag pin's to tell us when we have 32 bit's in the FIFO. Until the FIFO hit's HF on both FIFO's we inhibit the output clock. Then we know that the first bit is MSB (if we got the input logic right) .

We could even go completely asynchronous with a suitable XTAL clock on the output and switched XTAL capacitors to pull the crystal. It get's a bit much for a pure hardware solution at that point, but a 256 Bit 2228 might be long enough to not worry the glitches. Sounds like Operation Market Garden from here.

Thor

The issue with 74ACT2226 is that it's a rochester marketplace item. So ordering it requires large quantities and fhey do not sell to individuals. Everywhere else i see is a risk of fake ic.

The issue with 74ACT2226 is that it's a rochester marketplace item. So ordering it requires large quantities and fhey do not sell to individuals. Everywhere else i see is a risk of fake ic.

Well, there is that. But I like the simplicity of the control logic.

So where I end up is this.

A) Make a PCB with multiple options.

A.1) Have an SAA7220 Footprint. This can be filled with SAA7220 to give selectable 1X/4X at 1X digital signals or to fit a Raptorlightning FPGA Board published here for those who must have "FPGA or ain't mo betta". Could be a breakoff. Ideally the output is converted to slave clocking, but Raptorlightning seems to awol. A SRC419X can also be used and would allow a 32 X FS BCK option for 15 Bit Data (this was used in the CD-77 as format converter and optional up sampler).

A.2) Have the 74ACT2226 FIFO IIS2SIM option incorporated into PCB with the option to, bypass it. The divider chains for BCK and WCK can be shared with other options under A.1.

A.3) Have a CS8412 Footprint to accept different SPDIF Receiver options. AK4118 seems to be todays best option (other than WM8805), but we need to shut down the crystal oscillator and and not use crystal based frequency detection. Apparently if the Crystal Oscillator on the AK4118 is running it creates spurs in the MCK out, which are absent if it is shut down. AK4118 can be set to give a 512X (44.1/48) MCK. So, probably AK4118 designed into the board with CS8412 footprint for alternate Options (plus resistors for selection). A 1 X Pin would be useful, which CS8416 offers but AK4118 does not have it.

An option would be to use a DIR9001 while it remains in production strictly as sample rate detector, it is cheap enough and active with long supply.

A.4) have at least two Amanero Footprints, to allow for multiple sources, including USB, BT etc.

A.5) Have 74F74/74AC74/74AUC74 etc. logic (multiple footprints including TH) for reclocking and signal conditioning for 0...1.8V signal swing and slew rate limiting for either 64XIIS, 32XIIS (with SRC4190 with slave out) or 16XSIM from a range of sources with resistor jumper.

A.6) Add TDA1541 and supplies etc.

Thor

Last edited:

Feature creep ?

Backstops for EOL, Supply Chain Issues, Factory Fires etc.

Thor

A 1 X Pin would be useful, which CS8416 offers but AK4118 does not have it.

Ok, so I have been thinking, if there is a way to get a simple Sample Rate indication using discrete logic.

So, say, we use a 74HC4040 and a 24MHz crystal oscillator, we connect MR_bar to the WCK (with a buffer). We may already have the 24MHz somewhere, if not, many cheap options exist. Mouser lists 24MHz 50ppm under 1 USD in singles.

We can now count how many 24MHz clock pulses we have seen during 1/2 WCK.

For 352.8k (+/- 1%) we get a count of 33... 34 and for 384kHz (+/- 1%) we get a count of 30...31.

For 176.4k (+/- 1%) we get a count of 67... 38 and for 192kHz (+/- 1%) we get a count of 61...33.

For 88.2k (+/- 1%) we get a count of 134...137 and for 96kHz (+/- 1%) we get a count of 123...126.

For 44.1k (+/- 1%) we get a count of 269...274 and for 48kHz (+/- 1%) we get a count of 247...252.

To detect 44.1/48 we just need to look at the output Q4 if Q4 is L we have counted less 32 (48k) and if it is H we counted past 32 (44.1k). If we invert this we get L = 44.1k, H = 48k

A "NAND" of Q4 & Q3 detects a count of at least 48. If it is H, we have 8X, if it is L we have 4X, 2X or 1X.

A "NAND" of Q5 & Q4 detects a count of at least 96. If it is H, we have 4X, if it is L we have 2X or 1X.

A "NAND" of Q6 & Q5 detects a count of at least 192. If it is H, we have 2X, if it is L we have 1X.

We need to use a 4-way (or more) latch to latch the Outputs on rising edge of LRCK.

So we get a Hardware 4-Bit Sample rate indication of 44.1/48 and 1X/2X/4X/8X that is "sticky" unless the sample rate changes and only needs a single WCK feed.

WCK could be isolated via a 6N137 or similar opto-isolator. Many other options exist.

What can we do with this indication?

We can select the SINC EQ for non oversampling.

We can select BCK division to get the correct DEM Clock for TDA1541.

We can select between a fixed 45,1584MHz and 49.152MHz Low Noise Clock to drive a reclocker circuit (needs dual Flip-Flop's to avoid Meta Stability issues) that would alternatively be driven by the Amanero 44.1/48k indication.

We can light up Pretty LED's Lights...

Cost?

1 X 24MHz Oscillator

1 X 74HC4040 Counter

1 X 74HC00 Indication Logic

1 X 74HC173 Latch

Thor

Another approach for sample rate detection:

Actually, it is literally the same as I describe.

Start a timer with an LRCK period, latch the result. If the timer expired, the sample rate is "low" and if it still runs the sample rate is "hhigh".

Main difference is that what I propose can detect multiple sample rates (up to 3 with a 4-Way Flip Flop) and and it can reliably the difference between 44.1 & 48kHz. Making the circuit you show 3 times allows three different sample rates to be detected, as for the difference between 44.1 & 48kHz, that's something that I think is beyond RC levels of precision.

As a pure 1X detection is probably fine.

Thor

As a pure 1X detection is probably fine.

As a 74HC123 & 74HC74 have two sections each we can easily make a 1X/2X/4X detector. RC values may need empirical adjustment:

As the N Suffix on the outputs suggests, this is active low logic.

As both 74HCT123 sections will be switching with appx. FS decoupling and isolation of the power supplies is needed. On the + Side, there is no extra clock with an different clock frequency. And it is totally stand alone with on WCK supplied, no extra clocks etc. VERY SLOW logic can be used without problem.

As said, testing for 44.1/48kHz is not valid given tolerances and other factors. As alternative DIR9001 plus a 24.576MHz can do the same with a single IC and can detect 44.1/48k but cannot detect 2X/4X.

Divider Cascade and Crystal clock is able to detect everything but has a lot more switching noise.

Thor

I built the circuit shown above and tested treshold: there was a very distinct frequency where detection occurs. So if you could adjust RC precise enough it should be no problem to distinguish between 44.1 and 48k. Maybe use a trimmer for the RC...? Or are there fixed parts with low long term drift...? Also Amareno/JLsounds have pins that provide SR rate indication. Using 4118 would allow detection as well I guess...

And for your tasks maybe there is no need to detect 44.1 vs 48 based rates...?

And for your tasks maybe there is no need to detect 44.1 vs 48 based rates...?

I built the circuit shown above and tested treshold: there was a very distinct frequency where detection occurs.

Yes, but the frequency threshold is supply voltage and temperature dependent. Even with a perfect Resistor and capacitor there will be drift.

The cycle time of 176.4kHz is 5.66uS while 192kHz is 5.21uS. That is cutting it extremely fine for RC timing.

If we throw in extra dividers, why not use a crystal based reference?

So if you could adjust RC precise enough it should be no problem to distinguish between 44.1 and 48k. Maybe use a trimmer for the RC...? Or are there fixed parts with low long term drift...?

Good luck.

Also Amareno/JLsounds have pins that provide SR rate indication.

Yes, but that is USB only.

Using 4118 would allow detection as well I guess...

For that you need to do a few things. Software mode is essential, so we are looking at programming a CPU and controlling the AK4118 via SPI or I2C.

And we need to run the build in crystal oscillator which destroys all the nice low jitter. For AK4118 with low jitter, use hardware and no crystal.

It seems the AK4118 really gets low actual jitter on MCK if used right.

And for your tasks maybe there is no need to detect 44.1 vs 48 based rates...?

What I do personally is one thing.

Let me give you an example.

We use the SRC4190 or a long FIFO (74ACT2226/8) to convert 64FS IIS to something else. We also use a Cirrus "We jitter as jittery as we can" Logic CS8416 Receiver IC. So we get noise like Jitter at -70dBcbelow 20kHz.

We can in principle have a pair of crystal oscillators on the output side and select them to match the source base sample rate. If we can detect 176.4/192kHz accurate enough. We then use these to reclock the source BCK derived clock.

We normally expect < 50PPM for systems with clocks derived from Crystals, which for 2025 is almost anything.

So for 50 samples in 1 Million we can expect a 1 XTAL Clock shift of the clock to TDA1541.

For 512X Clocks that creates ~ 40nS peak-peak jitter. That's terrible right?

But what is the frequency of this jitter? Less than 0.5Hz for 1X, 1Hz for for 2X and 2Hz for 2X.

The exact frequency depends on the difference between the clocks. Now with such a "jitter" component our FFT's will show a 1st order slope, so at 20Hz the jitter plot will show 4nS PP for 192kHz, with rising frequency we drop. But not that this is really an articfact of the FFT.

What we should see is a huge spike at a very low frequency and then our crystal clock noise floor. We just need to adjust our FFT parameters and the falling slope disappears.

What is the generally acknowledged limit for jitter audibility with sine waves:

Now this is an artificial case, but it is clear that very low jitter frequencies allow much higher P-P jitter levels before becoming audible. Interesting note, the "knee" in the curve happens around where where the head shadow disappears and hearing uses time of arrival difference to determine location while where there is high sensitivity if where in effect amplitude difference drives localisation.

In practice this asynchronous "near sample frequency" relocking works really well. I tried it before on TDA1541 & CS8414 based DAC's. More precisely the infamous "Thomas" designs with a local clock and a 74HC4040 divider for BCK/WCK and manually switching for 44.1/48 and on off (off drive the 74HC4040 with MCK from the receiver. So 44.1kHz / 48kHz detection can be really important.

The alternative is the "microsoft" option of just ignoring the problem, maxing out the ASYNC reclocker frequency and using 114.285MHz as async reclocker.

There are a few options and we now have 8nS P-P Jitter with a frequency at high supersonic frequencies. This is in effect "jitter scrambling".

My experience with this method at lower frequencies (50MHz clock) was not that successful. It works best if we have some form of low speed PLL after.

But something I have not yet tried with is to reclock the source MCK and then divide the result to BCK/WCK. We get (with 114.285MHz) around a 1:5 ratio between clocks. So MCK is jittered at ~ 1/5th of it's clock frequency. Each division should lower the jitter. There may be room for some extra experimental circuitry on the board.

Thor

Ok, I still don't understand why there is no good solution by using a precision PLL (or similar IC) to generate a low jitter synced clock in case we don't want to use some kind of async clock. Are there no good ICs for that task available that allow us to clean out the incoming jitter?

Ok, I still don't understand why there is no good solution by using a precision PLL (or similar IC) to generate a low jitter synced clock in case we don't want to use some kind of async clock.

Got any suggestions? Something that doesn't need 100's of lines of code and has a (say) sub 10Hz corner and better than-90dBc @ 10Hz offset?

Are there no good ICs for that task available that allow us to clean out the incoming jitter?

There used to be ones, it has just become unavailable. Another decent one disappeared before that. A lot of stuff that looked interesting turns out to have usually jitter rejection corners in the kHz region and shitty LF Phase noise.

So now we need two VCXO's at 22.5792MHz and 24.576MHz and the necessary analogue PLL and all that.

The generic VCXO at Mouser all deliver -70dBc at 10Hz offset, that's not great. There are a few specialist devices but not easy to get. And designing a complete PLL that is low noise and locks fast etc. etc. does not to me seem like a good proposition.

So no, there are no ready OTS "jitter cleaner" IC's that are worth having.

Something like SRC4190 ASRC is our best bet then for something easy to use.

Set up as 1:1 (with the divider above) and add a cycle slip detector and if we "slip" too much switch into ASRC mode. we have ~64 Sample's worth of FIFO, so count say 32 slipped samples. But again, it starts with a precise detection of the incoming clock.

Or just use ASRC mode with clocks derived from 27MHz and up-sample everything to 210.9375kHz. A cheap and decent 27MHz crystal clock sits at ~ -90dBc for 10Hz offset. But the jitter rejection corner of the rate estimator is not that low either.

Non of these are ideal.

Ideal would be a Chip with a (say) 100MHz low phase noise crystal that takes in any frequency below 50MHz and has a 1Hz or 10Hz PLL corner, or an IC that takes two crystals, has internal switchable capacitors to trim the clock and a FIFO buffer plus some other control bits.

But nobody ever made anything like this.

Thor

I don't have suggestions regarding PLL parts.

But I would avoid ASRC and use the DIR9001 (or AK4118) for SPDIF, and use the reclocking stage also as the input selector. Optionally add a clock output to be able to sync a (modded) CD transport to the DAC. Or omit SPDIF at all and make it USB only.

But I would avoid ASRC and use the DIR9001 (or AK4118) for SPDIF, and use the reclocking stage also as the input selector. Optionally add a clock output to be able to sync a (modded) CD transport to the DAC. Or omit SPDIF at all and make it USB only.

I don't have suggestions regarding PLL parts.

Not surprised. There are some that can be made to have a low enough bandwidth, have the crystal VCXO on board etc.

They are not easy to use, are rather expensive need massive amounts of software.

But I would avoid ASRC

Note, I mainly will use the SRC419X in bypass mode, as FIFO and format converter. Actual SRC Mode is fallback in case of emergency.

An ASRC is tool and like all tools it needs care to use. Lets look at a relatively well understood ASRC:

Let's take the usual option, Crystal to REFCLK and divider from Crystal to BCKO and LRCKO.

Do we need to care about BCKI & LRCKI? The rate estimator is a 2nd order lowpass at 0.0005*FS/2. That 12/24/48Hz at 48/96/192kHz.

So we probably want to take care of reclocking BCKI. Asynchronous reclocking that scrambles jitter to >> 48kHz would probably do the trick of pushing Jitter out of band.

and use the DIR9001 (or AK4118) for SPDIF, and use the reclocking stage also as the input selector.

You want to re-clock with the lowest possible clock frequency. In fact, you want to run everything as slow as possible. You seem so hung up about input selection. It's the LEAST of your problems. Just don't take a 74HC157 please.

Optionally add a clock output to be able to sync a (modded) CD transport to the DAC.

What is "Seedee"?

Or omit SPDIF at all and make it USB only.

Well, most USB solutions have 100's to 1,000's ps of Jitter baked into the silicon. Plus, the digital isolators people use to isolate the earth loops are truly evil.

They all use a very high frequency carrier frequency made on chip with an RC oscillator to transmit the digital signals across the isolation barrier, capacitive, inductive coupling or GMR, all the same rot. Capacitive coupling radiates least, but jitter is horrible.

Using SPDIF allows a simple transformer to deal with the signal and we can use a second one to isolate MCK that we send back to the USB Module. A classic 100Base-T network transformer is great here.

Thor

- Home

- Source & Line

- Digital Source

- Simultaneous output Frontend for TDA1541 (and or Universal Multibit DAC) using discrete logic - Collaborators wanted